# ECE 2300 Digital Logic and Computer Organization Fall 2024

# **Topic 1: Digital Circuits**

School of Electrical and Computer Engineering Cornell University

revision: 2024-08-29-04-05

| 1 | Analog View of a Transistor              |      |  |  |  |  |  |  |  |  |  |  |  |

|---|------------------------------------------|------|--|--|--|--|--|--|--|--|--|--|--|

| 2 | Digital View of a Transistor             | 5    |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1. Binary Digital Abstraction          | . 5  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2. Switch-Level Model for a Transistor | . 6  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3. Transistor Networks                 | . 8  |  |  |  |  |  |  |  |  |  |  |  |

| 3 | CMOS Inverter                            | 10   |  |  |  |  |  |  |  |  |  |  |  |

| 4 | Simple Digital CMOS Circuits             |      |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1. Rules for Digital CMOS Circuits     | . 15 |  |  |  |  |  |  |  |  |  |  |  |

| 5 | More Complex Digital CMOS Circuits       | 16   |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.1. Multi-Input Digital Circuits        | . 16 |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.2. Multi-Stage Digital Circuits        | . 18 |  |  |  |  |  |  |  |  |  |  |  |

| 6 | Summary of Abstractions                  | 19   |  |  |  |  |  |  |  |  |  |  |  |

Copyright © 2024 Christopher Batten. All rights reserved. This handout was prepared by Prof. Christopher Batten at Cornell University for ECE 2300 / ENGRD 2300 Digital Logic and Computer Organization. Download and use of this handout is permitted for individual educational non-commercial purposes only. Redistribution either in part or in whole via both commercial or non-commercial means requires written permission.

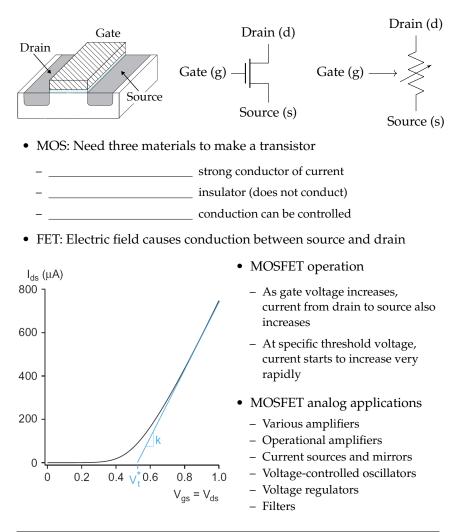

## 1. Analog View of a Transistor

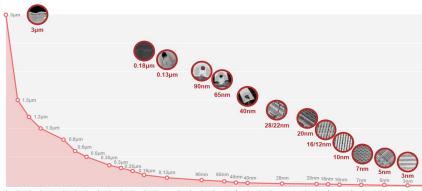

- **Transistors:** Invented by John Bardeen, Walter Brattain, and William Shockley at Bell Labs in 1947

- **Integrated Circuits:** Independently developed by Jack Kilby (at TI) and Robert Noyce (at Fairchild) in the 1950s; Noyce and Gordon Moore founded Intel in 1968

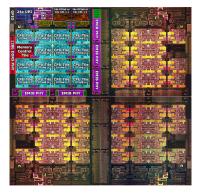

- Intel Saphire Rapids (2023)

- Number of transistors: 61 billion

- Technology node: Intel 7

## 2. Digital View of a Transistor

## 2.1. Binary Digital Abstraction

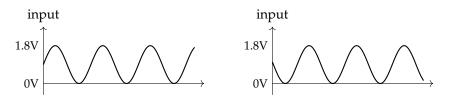

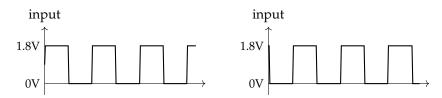

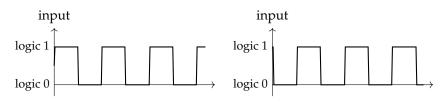

Analog circuits (continuous values are possible)

Binary digital circuits (only two specific values are possible)

Abstract low voltage as "logic 0" and high voltage as "logic 1"

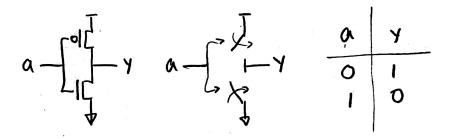

## 2.2. Switch-Level Model for a Transistor

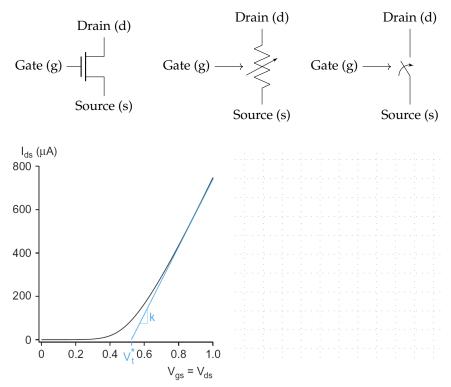

- Non-linear change in current make transistors act like switches

- If g = 0, then the switch is open

- If g = 1, then the switch is closed

- Two different kinds of MOSFETs

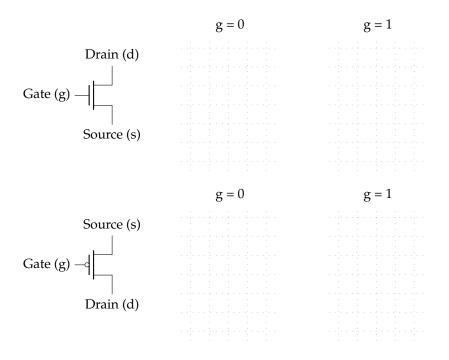

- **NMOS:** Closed when g = 1, open when g = 0, better at passing 0

- **PMOS:** Closed when g = 0, open when g = 1, better at passing 1

- NMOS and PMOS have complementary properties

- For same input, one will be on and one will be off

- Digital CMOS circuits combine NMOS and PMOS transistors

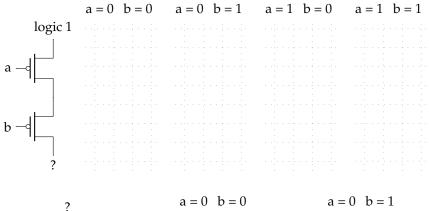

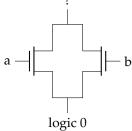

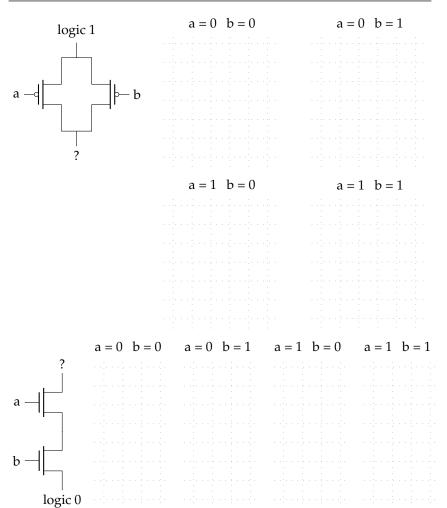

#### 2.3. Transistor Networks

#### $a = 1 \quad b = 0$

|  |  |  | , |  |  |  |  |  |  |

|--|--|--|---|--|--|--|--|--|--|

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  | ٠ |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

|  |  |  |   |  |  |  |  |  |  |

#### $a = 1 \ b = 1$

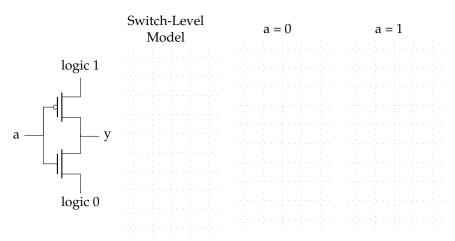

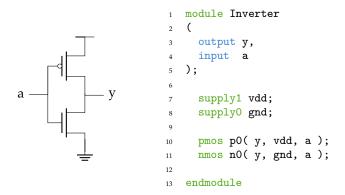

### 3. CMOS Inverter

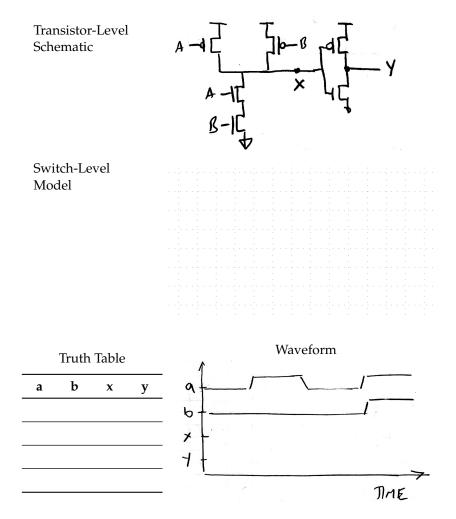

#### Truth Table

- Rows for all possible input values

- Specifies output for to given input values

#### Waveform

- Illustrates how outputs change over time for given input signals

- Various delay models are possible

#### Switch-Level Modeling in Verilog

- supply1 is used to create a "logic 1" power supply

- supply0 is used to create a "logic 0" ground

- pmos( drain, source, gate ) instantiates a PMOS transistor

- nnmos( drain, source, gate ) instantiates a PMOS transistor

- module/endmodule used to define a hardware module along with the corresponding input and output ports

https://www.edaplayground.com/x/LbpL

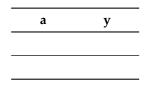

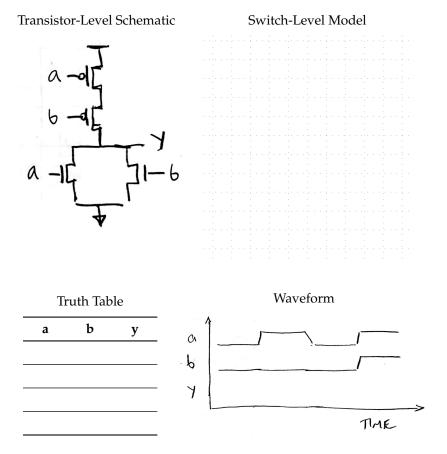

## 4. Simple Digital CMOS Circuits

https://www.edaplayground.com/x/wHkB

Switch-Level Model

#### Transistor-Level Schematic

# 4.1. Rules for Digital CMOS Circuits

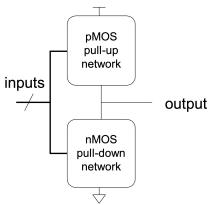

- Use NMOS and PMOS transistors such that:

- There should never be a direct path from Vdd to ground

- The output should never be floating

- Circuit is divided into two parts:

- Pull-up network exclusively uses PMOS transistors

- Pull-down network exclusively uses NMOS transistors

- The pull-up and pull-down networks are duals of each other

- Two transistors in series in the pull-down network will be in parallel in the pull-up network

- Two transistors in parallel in the pull-down network will be in series in the pull-up network

- Apply these rules hierarchically to subnets

- There should always be an equal number of PMOS and NMOS transistors

## 5. More Complex Digital CMOS Circuits

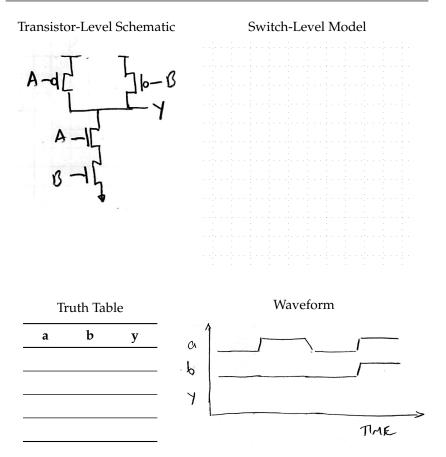

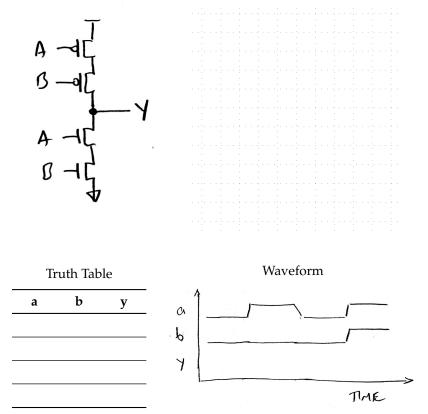

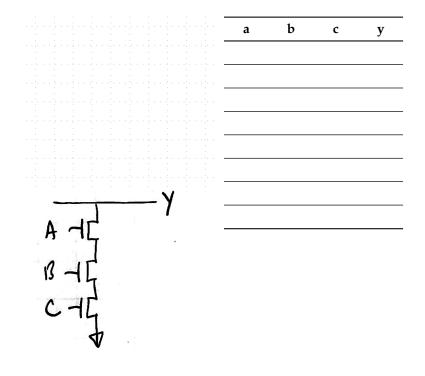

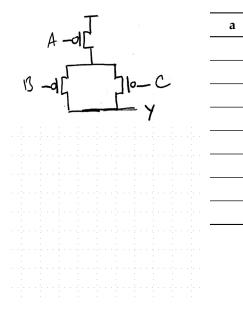

## 5.1. Multi-Input Digital Circuits

С

y

b

# Finish the circuit using the rules for digital CMOS circuits, then fill in the truth table.

## 5.2. Multi-Stage Digital Circuits

## 6. Summary of Abstractions