# ECE 2300 Digital Logic and Computer Organization Topic 6: Sequential Logic

http://www.csl.cornell.edu/courses/ece2300 School of Electrical and Computer Engineering Cornell University

revision: 2025-11-03-21-20

#### **List of Problems**

| 1 | Sequential Network 1 | 2  |

|---|----------------------|----|

| 2 | Sequential Network 2 | 6  |

| 3 | Sequential Network 3 | 9  |

| 4 | Sequential Network 4 | 12 |

| 5 | Sequential Network 5 | 14 |

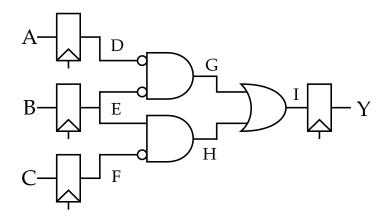

# Problem 1. Sequential Network 1

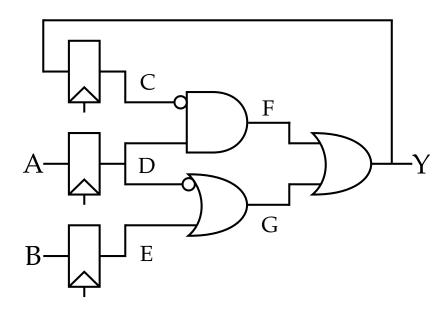

Complete the explicit-clock simulation table for the following sequential network.

| clk | A | В | С | D | Е | F | G | Н | I | Y |

|-----|---|---|---|---|---|---|---|---|---|---|

| 1   | 0 | 0 | 0 |   |   |   |   |   |   |   |

| 0   | 0 | 0 | 0 |   |   |   |   |   |   |   |

| 1   | 1 | 0 | 0 |   |   |   |   |   |   |   |

| 0   | 1 | 0 | 0 |   |   |   |   |   |   |   |

| 1   | 1 | 1 | 0 |   |   |   |   |   |   |   |

| 0   | 1 | 1 | 0 |   |   |   |   |   |   |   |

| 1   | 1 | 1 | 1 |   |   |   |   |   |   |   |

| 0   | 1 | 1 | 1 |   |   |   |   |   |   |   |

| 1   | 0 | 0 | 1 |   |   |   |   |   |   |   |

| 0   | 0 | 0 | 1 |   |   |   |   |   |   |   |

| 1   | 0 | 0 | 0 |   |   |   |   |   |   |   |

| 0   | 0 | 0 | 0 |   |   |   |   |   |   |   |

NetID: \_

Complete the timing diagram for the sequential gate network utilizing the delay model to the right. Illustrate both the propagation and contamination delays in the timing diagram. Note: Use NOT-Gates for inverted inputs.

|              | $t_{pd}$ | $t_{cd}$ |

|--------------|----------|----------|

| NOT          | $1\tau$  | $1\tau$  |

| AND2         | $3\tau$  | $1\tau$  |

| OR2          | $4\tau$  | $1\tau$  |

| $FF(t_{cq})$ | 9τ       | 2τ       |

| FF $(t_{setup})$ | 10τ |

|------------------|-----|

| FF $(t_{hold})$  | 1τ  |

| $T_C$            | 30τ |

#### Prof. Batten's Solution

https://vod.video.cornell.edu/media/t/1\_uh9aao0s

| ECE 2200 | Digital | I agia am | 1 Comments | Ougan  | ization  |

|----------|---------|-----------|------------|--------|----------|

| ECE 2300 | Digitut | Logic and | d Computer | Organi | ızuııorı |

Use the following table to list every constraint which must be satisfied to ensure correct operation of this gate-level network. Start by labeling the two possible constraints at the top of the table. You do not need to include the unit  $\tau$  in your constraints. Each path should be specified with just the start and end points of the path. You do not need to list the gates along the path. Assume paths that start at an input port or end at an output port are unconstrained. Each constraint should be expressed as an inequality. If the constraint is satisfied use  $\geq$  or  $\leq$ . If the constraint is not satisified use  $\geq$  or  $\leq$ . You must show each delay component in the inequality along with the the final sum. Circle any constraints which are not statisified and would result in a timing violation. *Note: Use NOT-Gates for inverted inputs.*

| Path Start Point | Path End Point | Constraint | Constraint |

|------------------|----------------|------------|------------|

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

| Are there any unsatisfied constraints (i.e., timing violations)?                                                      |

|-----------------------------------------------------------------------------------------------------------------------|

| Identify the critical path. Describe its path and calculate its setup time slack.                                     |

|                                                                                                                       |

| Identify the short path. Describe its path and calculate its hold time slack.                                         |

|                                                                                                                       |

| What is the minimum clock period (T <sub>C</sub> ) that would still ensure correct operation?                         |

|                                                                                                                       |

| What is the maximum clock frequency that would still ensure correct operation? Presume $1\tau$ to be $1\mathrm{ns}$ . |

|                                                                                                                       |

|                                                                                                                       |

#### **Computing Slack**

Slack measures the margin by which the timing constraints are met (positive slack) or missed (negative slack). For the setup constraint ( $T_C \ge t_{pd,cq} + t_{pd,comb} + t_{setup}$ ), the setup slack is computed using the following formula:

$$t_{slack, setup} = T_C - t_{pd, cq} - t_{pd, comb} - t_{setup}$$

For the hold constraint ( $t_{hold} \le t_{cd,cq} + t_{cd,comb}$ ), the hold slack is computed using the following formula:

$$t_{slack,hold} = t_{cd,cq} + t_{cd,comb} - t_{hold}$$

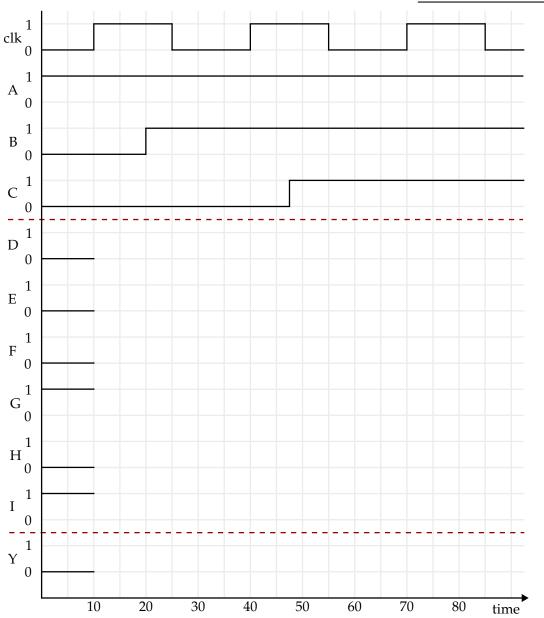

#### Problem 2. Sequential Network 2

Complete the implicit-clock simulation table for the following sequential network. *Note: Due to the logic in the subsequent stage, a larger output flip-flop is used in this stage (with different setup and hold parameters).*

| A | В | С | D | Е | F | G | Н | I | J | K | Y |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 |   |   |   |   |   |   |   |   |   |

| 0 | 1 | 1 |   |   |   |   |   |   |   |   |   |

| 0 | 1 | 0 |   |   |   |   |   |   |   |   |   |

| 1 | 1 | 1 |   |   |   |   |   |   |   |   |   |

| NetID: |

|--------|

|--------|

Use the following table to list every constraint which must be satisfied to ensure correct operation of this gate-level network. Start by labeling the two possible constraints at the top of the table. You do not need to include the unit  $\tau$  in your constraints. Each path should be specified with just the start and end points of the path. You do not need to list the gates along the path. Assume paths that start at an input port or end at an output port are unconstrained. Each constraint should be expressed as an inequality. If the constraint is satisfied use  $\geq$  or  $\leq$ . If the constraint is not satisified use  $\not\geq$  or  $\not\leq$ . You must show each delay component in the inequality along with the the final sum. Circle any constraints which are not statisified and would result in a timing violation.

|                               | $t_{pd}$ | $t_{cd}$       |

|-------------------------------|----------|----------------|

| NOT                           | $1\tau$  | 1τ             |

| NAND2                         | $2\tau$  | $1\tau$        |

| AND2                          | $3\tau$  | $1\tau$        |

| OR2                           | $4\tau$  | $1\tau$        |

| $FF(t_{cq})$                  | 9τ       | $2\tau$        |

|                               |          |                |

| FF-Input ( $t_{in,setup}$ )   | 10       | )τ             |

| FF-Input $(t_{in,hold})$      | 1        | τ              |

| FF-Output ( $t_{out,setup}$ ) | 20       | )τ             |

| FF-Output ( $t_{out,hold}$ )  | 5        | τ              |

| $T_C$                         | 45       | <del>5</del> τ |

| Path Start Point | Path End Point | Constraint | Constraint |

|------------------|----------------|------------|------------|

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

| Are there any unsatisfied constraints (i.e., timing violations)?                                                                                                     |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Identify the critical path. Describe its path and calculate its setup time slack.                                                                                    |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

| Identify the short path. Describe its path and calculate its hold time slack.                                                                                        |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

| What is the minimum clock period (T <sub>C</sub> ) and the maximum clock frequency that would still ensure correct operation? Presume $1\tau$ to be $1\mathrm{ns}$ . |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

| In case the hold constraint was violated: How can this be fixed? Can this fix be performed after tapeout? Note: Draw the potential fix in the block diagram.         |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                      |  |  |  |  |

#### Stephen's Solution

https://vod.video.cornell.edu/media/ECE+2300+Topic+6%2C+Practice+Problem+2/1\_vvqvf4my

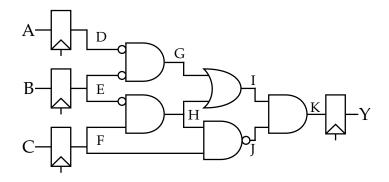

# Problem 3. Sequential Network 3

Complete the implicit-clock simulation table for the following sequential network.

| A | В | С | D | Е | F | G | Н | I | J | Y |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 |   |   |   |   |   |   |   |   |

| 0 | 1 | 0 |   |   |   |   |   |   |   |   |

| 1 | 1 | 0 |   |   |   |   |   |   |   |   |

| 1 | 1 | 0 |   |   |   |   |   |   |   |   |

| 0 | 1 | 1 |   |   |   |   |   |   |   |   |

| 0 | 1 | 1 |   |   |   |   |   |   |   |   |

| 1 | 1 | 1 |   |   |   |   |   |   |   |   |

| 0 | 1 | 0 |   |   |   |   |   |   |   |   |

| NetID: |  |  |

|--------|--|--|

|        |  |  |

Use the following table to list every constraint which must be satisfied to ensure correct operation of this gate-level network. Start by labeling the two possible constraints at the top of the table. You do not need to include the unit  $\tau$  in your constraints. Each path should be specified with just the start and end points of the path. You do not need to list the gates along the path. Assume paths that start at an input port or end at an output port are unconstrained. Each constraint should be expressed as an inequality. If the constraint is satisfied use  $\geq$  or  $\leq$ . If the constraint is not satisfied use  $\not\geq$  or  $\not\leq$ . You must show each delay component in the inequality along with the the final sum. Circle any constraints which

| ·               | $t_{pd}$ | $t_{cd}$ |  |

|-----------------|----------|----------|--|

| NOT             | $1\tau$  | $1\tau$  |  |

| AND2            | $3\tau$  | $1\tau$  |  |

| XOR2            | $7\tau$  | $1\tau$  |  |

| $FF(t_{cq})$    | 9τ       | $2\tau$  |  |

|                 |          |          |  |

| $FF(t_{setup})$ | 10       | )τ       |  |

| $FF(t_{hold})$  | $1\tau$  |          |  |

| $T_C$           | 27τ      |          |  |

|                 |          |          |  |

are not statisified and would result in a timing violation. Note: Use NOT-Gates for inverted inputs.

| Path Start Point | Path End Point                             | Constraint | _ Constraint |

|------------------|--------------------------------------------|------------|--------------|

|                  |                                            |            |              |

|                  |                                            |            |              |

|                  |                                            |            |              |

|                  |                                            |            |              |

|                  |                                            |            |              |

| Are there an     | y unsatisfied constraints (i.e., timing vi | olations)? |              |

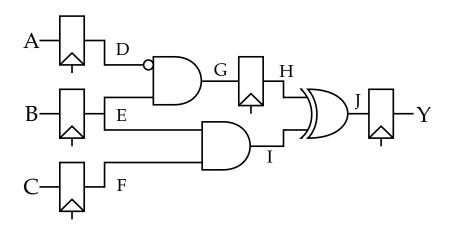

# **Problem 4. Sequential Network 4**

Complete the implicit-clock simulation table for the following sequential network.

| A | В | С | D | E | F | G | Y |

|---|---|---|---|---|---|---|---|

| 0 | 0 |   |   |   |   |   |   |

| 1 | 0 |   |   |   |   |   |   |

| 1 | 0 |   |   |   |   |   |   |

| 1 | 1 |   |   |   |   |   |   |

| 0 | 0 |   |   |   |   |   |   |

Use the following table to list every constraint which must be satisfied to ensure correct operation of this gate-level network. Start by labeling the two possible constraints at the top of the table. You do not need to include the unit  $\tau$  in your constraints. Each path should be specified with just the start and end points of the path. You do not need to list the gates along the path. Assume paths that start at an input port or end at an output port are unconstrained. Each constraint should be expressed as an inequality. If the constraint is satisfied use  $\geq$  or  $\leq$ . If the constraint is not satisified use  $\not\geq$  or  $\not\leq$ . You must show each delay component in the inequality along with the the final sum. Circle any constraints which

| 1τ<br>3τ<br>4τ | 1τ<br>1τ<br>1τ |  |

|----------------|----------------|--|

| $4\tau$        | $1\tau$        |  |

|                |                |  |

| _              |                |  |

| 9τ             | $2\tau$        |  |

|                |                |  |

| $10\tau$       |                |  |

| $1\tau$        |                |  |

| 30τ            |                |  |

|                | 1′             |  |

are not statisified and would result in a timing violation. Note: Use NOT-Gates for inverted inputs.

| n Start Point | Path End Point                  | Constraint                                                                                          | Constrair      |

|---------------|---------------------------------|-----------------------------------------------------------------------------------------------------|----------------|

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

| Are there ar  | ny unsatisfied constraints (i.e | e., timing violations)?                                                                             |                |

|               |                                 |                                                                                                     |                |

| Identify the  | critical nath. Describe its n   | ath and calculate its setup time slack.                                                             |                |

| rucitiny the  | critical path. Describe its po  | and carculate its setup time stack.                                                                 |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

| I domtify the | shout math. Docariba its mat    | h and salaulata ita hald tima alask                                                                 |                |

| identity the  | short path. Describe its pat    | h and calculate its hold time slack.                                                                |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

|               |                                 | \ \d_{\dagger}                                                                                      |                |

|               | -                               | <ul> <li>that would still ensure correct oper<br/>till ensure correct operation? Presume</li> </ul> |                |

|               | ioun iroquoney unu mounu s      | op cannon a recursion                                                                               | 11 10 00 11101 |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

|               |                                 |                                                                                                     |                |

# Problem 5. Sequential Network 5

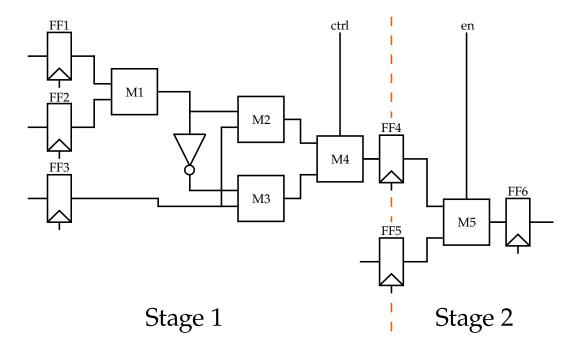

In this problem, we will inspect a two stage network containing the abstract combinational modules M1-M5.

Use the following table to list every constraint which must be satisfied to ensure correct operation of this gate-level network. Start by labeling the two possible constraints at the top of the table. You do not need to include the unit  $\tau$  in your constraints. Each path should be specified with just the start and end points of the path. You do not need to list the gates along the path. Assume paths that start at an input port or end at an output port are unconstrained. Each constraint should be expressed as an inequality. If the constraint is satisfied use  $\geq$  or  $\leq$ . If the constraint is not satisified use  $\not\geq$  or  $\not\leq$ . You must show each delay component in the inequality along with the the final sum. Circle any constraints which are not statisified and would result in a timing violation.

|                 | $t_{pd}$ | $t_{cd}$ |

|-----------------|----------|----------|

| NOT             | $1\tau$  | $1\tau$  |

| M1              | $5\tau$  | $1\tau$  |

| M2              | $10\tau$ | $1\tau$  |

| M3              | $12\tau$ | $1\tau$  |

| M4              | $7\tau$  | $1\tau$  |

| M5              | $17\tau$ | $1\tau$  |

| $FF(t_{cq})$    | 9τ       | $2\tau$  |

|                 |          |          |

| $FF(t_{setup})$ | $10\tau$ |          |

| $FF(t_{hold})$  | $1\tau$  |          |

| $T_C$           | 40τ      |          |

| Path Start Point | Path End Point | Constraint | Constraint |

|------------------|----------------|------------|------------|

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |

|                  |                |            |            |