## Sequential Logic

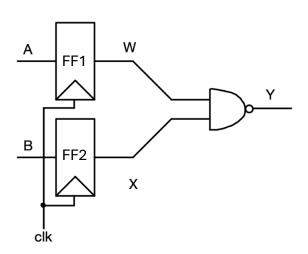

For the following problems complete the simulation table. Assume zero delay model.

1.

| clk | А | В | W | Х | Y |

|-----|---|---|---|---|---|

| 0   | 0 | 0 |   |   |   |

| 1   | 1 | 0 |   |   |   |

| 0   | 1 | 1 |   |   |   |

| 1   | 0 | 1 |   |   |   |

| 0   | 0 | 0 |   |   |   |

| 1   | 1 | 1 |   |   |   |

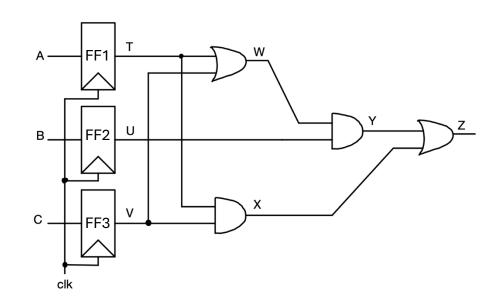

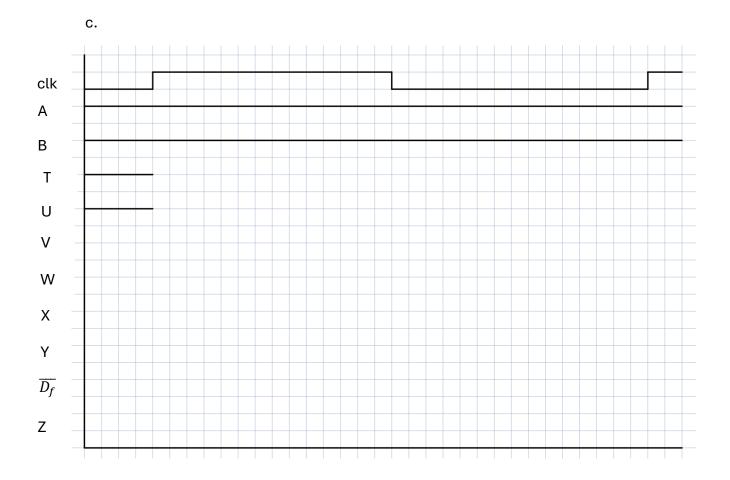

| clk | А | В | С | Т | U | V | W | Х | Y | Z |

|-----|---|---|---|---|---|---|---|---|---|---|

| 0   | 0 | 0 | 0 |   |   |   |   |   |   |   |

| 1   | 1 | 0 | 0 |   |   |   |   |   |   |   |

| 0   | 1 | 1 | 0 |   |   |   |   |   |   |   |

| 1   | 0 | 1 | 1 |   |   |   |   |   |   |   |

| 0   | 0 | 1 | 0 |   |   |   |   |   |   |   |

| 1   | 1 | 1 | 1 |   |   |   |   |   |   |   |

| 0   | 1 | 0 | 1 |   |   |   |   |   |   |   |

| 1   | 1 | 1 | 0 |   |   |   |   |   |   |   |

| 0   | 1 | 0 | 1 |   |   |   |   |   |   |   |

| 1   | 0 | 0 | 1 |   |   |   |   |   |   |   |

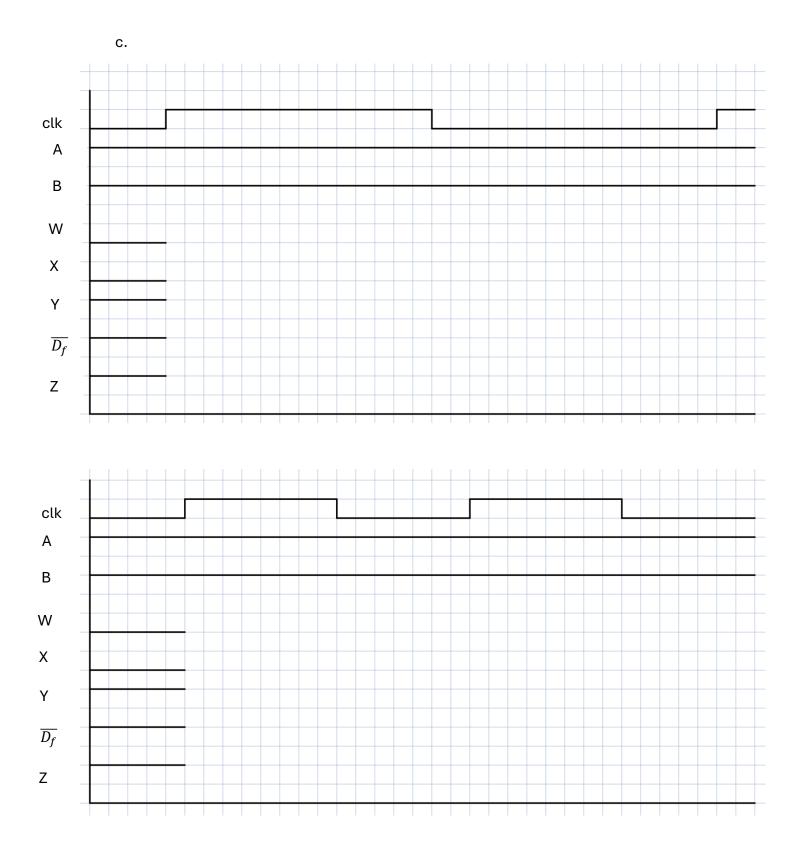

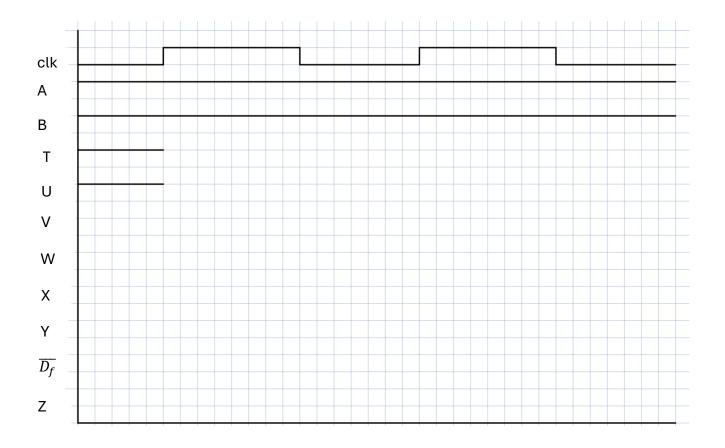

For the following problems, you will be asked to analyze a sequential gate-level network. Each problem you will be asked to write down all the paths, label the short and critical path(s), compute the minimum clock period given the delay model that is provided, as well as compute hold time constraint using the delay model that is provided. Use  $\overline{D_f}$  only for the waveform diagrams.

| 3.                                                 | Gate                                         | t <sub>pd</sub> | t <sub>cd</sub> |

|----------------------------------------------------|----------------------------------------------|-----------------|-----------------|

|                                                    | NAND2                                        | 2τ              | 1τ              |

| Y FF3 Z                                            | 1-bit FF Clock-to-Q                          | 9τ              | -               |

|                                                    | 1-bit FF Setup                               | 10τ             | -               |

|                                                    | Input Clock-to-Port                          | 0τ              | -               |

| clk                                                | Output Port Setup                            | 0τ              | -               |

| Path Delay of Each Component on Path $t_{pd,tota}$ | <i>l t<sub>cd,total</sub></i> Critical Path? | Short F         | Path?           |

|                                                    |                                              |                 |                 |

|                                                    |                                              |                 |                 |

- a. Compute the hold time,  $t_{hold}$ .

- b. What is the minimum clock period  $T_c$  in units of  $\tau$ ?

|      |                                 |                       | Gate                  |                | $t_{pd}$ | t <sub>cd</sub> |

|------|---------------------------------|-----------------------|-----------------------|----------------|----------|-----------------|

|      |                                 |                       | OR2                   |                | 4τ       | 1τ              |

|      |                                 | FF3                   | AND2                  |                | 3τ       | 1τ              |

| ]    |                                 | $\square$             | 1-bit F               | F Clock-to-Q   | 9τ       | -               |

| _    |                                 | clk                   | 1-bit F               | F Setup        | 10τ      | -               |

|      |                                 |                       | Input                 | Clock-to-Port  | 0τ       | -               |

|      | clk                             |                       | Outpu                 | ıt Port Setup  | 0τ       | -               |

| Path | Delay of Each Component on Path | t                     | <i>t</i>              | Critical Path? | Short P  | ath?            |

| Path | Delay of Each Component on Path | t <sub>pd,total</sub> | t <sub>cd,total</sub> | Critical Path? | Short Pa | ath?            |

| Path | Delay of Each Component on Path | t <sub>pd,total</sub> | t <sub>cd,total</sub> | Critical Path? | Short Pa | ath?            |

| Path | Delay of Each Component on Path | t <sub>pd,total</sub> | t <sub>cd,total</sub> | Critical Path? | Short F  |                 |

- a. Compute the hold time,  $t_{hold}$ . b. What is the minimum clock period  $T_c$  in units of  $\tau$ ?

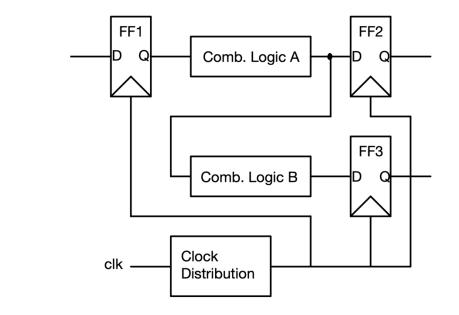

| Component       | t <sub>pd</sub> | t <sub>cd</sub> | Setup<br>Time | Hold<br>Time | Min Clock<br>Distribution Delay | Max Clock<br>Distribution Delay |

|-----------------|-----------------|-----------------|---------------|--------------|---------------------------------|---------------------------------|

| FF1             | 1               | 4               | 2             | 1            | 2                               | 3                               |

| FF2             | 4               | 6               | 2             | 0            | 3                               | 5                               |

| FF3             | 2               | 3               | 4             | 2            | 1                               | 2                               |

| Comb Logic<br>A | 1               | 4               | -             | -            | -                               | -                               |

| Comb Logic<br>B | 4               | 6               | -             | -            | -                               | -                               |

a. Calculate the worst-case clock skew between FF1 and FF2, and between FF1 and FF3, when considering FF2 and FF3 setup time.

b. Determine the fastest cycle time at which the circuit can operate. Justify your answer by analyzing all possible paths in your answer.

c. Calculate the worst-case clock skew between FF1 and FF2, and between FF1 and FF3 when considering FF2 and FF3 hold time.

d. Does this circuit have a hold time problem? Justify you answer by analyzing al possible paths in your answer.

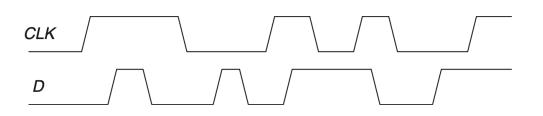

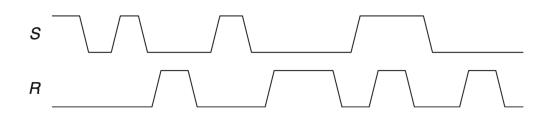

6. (Exercise 3.2, H&H RISC-V Edition) Given the input waveforms shown below, sketch the output, Q, of an SR latch.

7. (Exercise 3.3/3.5, H&H RISC-V Edition) Given the input waveforms shown below, sketch the output, Q of a D latch and of a D flip-flop.