# ECE 4750 Computer Architecture, Fall 2023 Tutorial 4: Verilog Hardware Description Language

# School of Electrical and Computer Engineering Cornell University

revision: 2023-09-03-16-12

| 1                        | Introduction                                            |                                                           |    |  |  |  |  |

|--------------------------|---------------------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|

| 2                        | Veri                                                    | Verilog Modeling: Synthesizable vs. Non-Synthesizable RTL |    |  |  |  |  |

| 3                        | Verilog Basics: Data Types, Operators, and Conditionals |                                                           |    |  |  |  |  |

|                          | 3.1                                                     | Hello World                                               | 4  |  |  |  |  |

|                          | 3.2                                                     | Logic Data Types                                          | 5  |  |  |  |  |

|                          | 3.3                                                     | Shift Operators                                           | 10 |  |  |  |  |

|                          | 3.4                                                     | Arithmetic Operators                                      | 12 |  |  |  |  |

|                          | 3.5                                                     | Relational Operators                                      | 13 |  |  |  |  |

|                          | 3.6                                                     | Concatenation Operators                                   | 15 |  |  |  |  |

|                          | 3.7                                                     | Enum Data Types                                           | 16 |  |  |  |  |

|                          | 3.8                                                     | Struct Data Types                                         | 18 |  |  |  |  |

|                          | 3.9                                                     | Ternary Operator                                          | 19 |  |  |  |  |

|                          | 3.10                                                    | If Statements                                             | 21 |  |  |  |  |

|                          | 3.11                                                    | Case Statements                                           | 22 |  |  |  |  |

|                          | 3.12                                                    | Casez Statements                                          | 23 |  |  |  |  |

| 4 Registered Incrementer |                                                         | istered Incrementer                                       | 23 |  |  |  |  |

|                          | 4.1                                                     | RTL Model of Registered Incrementer                       | 24 |  |  |  |  |

|                          | 4.2                                                     | Simulating a Model using verilator                        | 26 |  |  |  |  |

|                          | 4.3                                                     | Reusing a Model with Structural Composition               | 28 |  |  |  |  |

|                          | 4.4                                                     | Parameterizing a Model with Static Elaboration            | 29 |  |  |  |  |

| 5                        | Sort                                                    | Unit                                                      | 35 |  |  |  |  |

|                          | 5.1                                                     | Flat Sorter Implementation                                | 36 |  |  |  |  |

|                          | 5.2                                                     | Using Verilog Line Traces                                 | 38 |  |  |  |  |

|                          | 5.3                                                     | Structural Sorter Implementation                          | 39 |  |  |  |  |

|                          |                                                         |                                                           |    |  |  |  |  |

| 6 | 6 Greatest Common Divisor: Verilog Design Example |                                       |    |  |  |  |

|---|---------------------------------------------------|---------------------------------------|----|--|--|--|

|   | 6.1                                               | Control/Datapath Split Implementation | 42 |  |  |  |

#### 1. Introduction

This tutorial briefly reviews the basics of the Verilog hardware description language. In this class, we will primarily be using the open-source tool Verilator (verilator) as our Verilog simulator. We will also be using GTKWave (gtkwave) for viewing waveforms and lccv to generate coverage reports.

To follow along with the tutorial, access the ECE computing resources, and type the commands without the % character. In addition to working through the commands in the tutorial, you should also try the more open-ended tasks marked with the  $\star$  symbol.

Before you begin, make sure that you have **sourced the setup-ece4750.sh script** or that you have added it to your .bashrc script, which will then source the script every time you login. Sourcing the setup script sets up the environment required for this class.

You get the code for tutorial by on the course canvas site.

To get started, access an ecelinux machine and download a local copy of the tutorial files from the course website and extract it into a directory titled sim with the following commands:

```

% source setup-ece4750.sh

% mkdir -p ${HOME}/ece4750

% cd ${HOME}/ece4750

% wget https://www.csl.cornell.edu/courses/ece4750/handouts/ece4750-tut-verilog.tar.gz

% tar -xvzf ece4750-tut-verilog.tar.gz

% cd sim

% make setup

```

# 2. Verilog Modeling: Synthesizable vs. Non-Synthesizable RTL

Verilog is a powerful language that was originally intended for building simulators of hardware as opposed to models that could automatically be transformed into hardware (e.g., synthesized to an FPGA or ASIC). Given this, it is very easy to write Verilog code that does not actually model any kind of realistic hardware. Indeed, we actually need this feature to be able to write clean and productive assertions and line tracing. Non-synthesizable Verilog modeling is also critical when implementing test harnesses. So students must be very diligent in actively deciding whether or not they are writing synthesizable register-transfer-level models or non-synthesizable code. Students must always keep in mind what hardware they are modeling and how they are modeling it!

Students' design work will almost exclusively use synthesizable register-transfer-level (RTL) models. It is acceptable to include a limited amount of non-synthesizable code in students' designs for the sole purpose of debugging, assertions, or line tracing. If the student includes non-synthesizable code in their actual design (i.e., not the test harness), they must explicitly demarcate this code by wrapping it in 'ifndef SYNTHESIS and 'endif. This explicitly documents the code as non-synthesizable and aids automated tools in removing this code before synthesizing the design. If at any time students are unclear about whether a specific construct is allowed in a synthesizable concurrent block, they should ask a member of the course staff, as the penalty for incorrect usage of non-synthesizable code starts at 25% in labs

Appendix A includes a table that outlines which Verilog constructs are allowed in synthesizable RTL, which constructs are allowed in synthesizable RTL with limitations, and which constructs are explicitly not allowed in synthesizable RTL. There are no limits on using the Verilog preprocessor, since the preprocessing step happens at compile time.

# 3. Verilog Basics: Data Types, Operators, and Conditionals

We will begin by writing some very basic code to explore Verilog data types, operators, and conditionals. We will not be modeling actual hardware yet; we are just experimenting with the language.

#### 3.1. Hello World

Create a new Verilog source file named utb\_hello-world.v with the contents shown in Figure 1 using your favorite text editor. A module is the fundamental hardware building block in Verilog, but for now we are simply using it to encapsulate an initial block. The initial block specifies code which should be executed "at the beginning of time" when the simulator starts. Since real hardware cannot do anything "at the beginning of time" initial blocks are not synthesizable and you should not use them in the synthesizable portion of your designs. However, initial blocks can be useful

```

include "vc/trace.v"

module top( input logic clk, input logic linetrace );

initial begin

sdisplay( "Hello World!" );

finish();

end

endmodule

```

Code at tut4\_verilog/utb\_ex-basics-hello-world.v

**Figure 1: Verilog Basics: Display Statement –** The obligatory "Hello, World!" program to compiling a basic Verilog program.

| Log                             | ical Operators                                                          | Reduction Operators              |                                                                            |   | <b>Relational Operators</b>             |                                                               |  |

|---------------------------------|-------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------|---|-----------------------------------------|---------------------------------------------------------------|--|

| &<br> <br> <br> <br> -<br> -    | bitwise AND<br>bitwise OR<br>bitwise XOR<br>bitwise XNOR<br>bitwise NOT | *                                | reduce via AND reduce via NAND reduce via OR reduce via NOR reduce via XOR |   | ==<br>!=<br>><br>>=<br><                | equal not equal greater than greater than or equals less than |  |

| &&<br>  <br>!                   | boolean AND<br>boolean OR<br>boolean NOT                                | reduce via XNOR  Shift Operators |                                                                            | _ | <= less than or equals  Other Operators |                                                               |  |

| Arithmetic Operators + addition |                                                                         | >><br><<<br>>>>                  | shift right<br>shift left<br>arithmetic shift right                        | _ | {}<br>{N{}                              | concatenate<br>} replicate N times                            |  |

| _                               | subtraction                                                             |                                  |                                                                            |   |                                         |                                                               |  |

**Table 1: Table of Verilog Operators** – Not all Verilog operators are shown, just those operators that are acceptable for use in the synthesizable RTL portion of students' designs.

for test harnesses and when experimenting with the Verilog language. The initial block in Figure 1 contains a single call to the display system task which will output the given string to the console.

We will be using verilator to compile Verilog models into simulators in the beginning of this tutorial before we turn our attention to using Verilator. You can make and run utb\_hello-world.v as follows.

```

% cd ${HOME}/ece4750/sim/tut4_verilog % make utb_hello-world.v

```

★ *To-Do On Your Own:* Edit the string that is displayed in this simple program, recompile, and rerun the simulator.

#### 3.2. Logic Data Types

To understand any new modeling language we usually start by exploring the primitive data types for representing values in a model. Verilog uses a combination of the wire and reg keywords which interact in subtle and confusing ways. SystemVerilog has simplified modeling by introducing the logic data type. We will be exclusively using logic as the general-purpose, hardware-centric data type for modeling a single bit or multiple bits. Each bit can take on one of four values: 0, 1, X, Z. X is used to represent unknown values (e.g., the state of a register on reset). Z is used to represent high-impedance values. Although we will use variables with X values in this course, we will not use variables with Z values (although you may see Z values if you forget to connect an input port of a module).

Table 1 shows the operators that we will be primarily using in this course. Note that Verilog and SystemVerilog support additional operators including \* for multiplication, / for division, % for modulus, \*\* for exponent, and ===/!=== for special equality checks. There may occasionally be reasons to use one of these operators in your assertion or line tracing logic. However, these operators are either not synthesizable or synthesize poorly, so students are not allowed to use these operators in the synthesizable portion of their designs.

```

`include "vc/trace.v"

module top ( input logic clk, input logic linetrace );

// Declare single-bit logic variables.

5

logic a;

7

logic b;

logic c;

10

initial begin

11

12

13

// Single-bit literals

14

a = 1'b0; $\display(\"1'b0 = \%x \", a);

16

17

a = 1'bz; $display("1'bz = %x", a);

18

19

20

// Bitwise logical operators for doing AND, OR, XOR, and NOT

21

a = 1'b0;

22

b = 1'b1;

23

24

c = a & b; $display( "0 & 1 = %x ", c);

25

c = a | b; $display( "0 | 1 = \frac{1}{x} ", c);

27

28

30

// Bitwise logical operators for doing AND, OR, XOR, and NOT with X

31

a = 1'b0;

32

b = 1'bx;

34

c = a \& b; $display( "0 & x = %x ", c);

35

c = a \mid b; $display( "0 | x = \%x ", c );

36

c = a ^b; $display( "0 ^ x = %x ", c );

37

$display( "~x

c = ~b;

= %x ", c);

38

39

// Boolean logical operators

41

a = 1'b0;

42

b = 1'b1;

43

44

c = a \&\& b; $display("0 \&\& 1 = %x", c);

45

c = a || b; $display( "0 || 1 = %x ", c );

46

$display( "!1 = %x ", c );

c = !b;

47

48

$finish();

49

50

end

52 endmodule

```

Code at tut4-verilog/utb\_ex-basics-logic-sbit.v

**Figure 2: Verilog Basics: Single-Bit Logic and Logical Operators –** Experimenting with single-bit logic variables and literals, logical bitwise operators, and logical boolean operators.

Figure 2 shows an example program that illustrates single-bit logic types. Create a new Verilog source file named utb\_logic-sbit.v and copy some or all of this code. Compile this source file and run the resulting simulator.

Lines 13–16 illustrate how to write single-bit literals to express constant values. Lines 23–26 illustrate basic bitwise logical operators (&, |, ^, ~). Whenever we consider an expression in Verilog, we should

always ask ourselves, "What will happen if one of the inputs is an X?" Lines 33–36 illustrate what happens if the second operand is an X for bitwise logical operators. Recall that X means "unknown". If we OR the value 0 with an unknown value we cannot know the result. If the unknown value is 0, then the result should be 0, but if the unknown value is 1, then the result should be 1. So Verilog specifies that in this case the value of the expression is X. Notice what happens if we AND the value 0 with an unknown value. In this case, we can guarantee that for any value for the second operand the result will always be 0, so Verilog specifies the value of the expression is 0.

In addition to the basic bitwise logical operators, Verilog also defines three boolean logical operators (&&, ||, !). These operators are effectively the same as the basic logical operators (&, |,  $^{\sim}$ ) when operating on single-bit logic values. The difference is really in the designer's intent. Using &&, ||,! suggests that the designer is implementing a boolean logic expression as opposed to doing low-level bit manipulation.

★ *To-Do On Your Own:* Experiment with more complicated multi-stage logic expressions by writing the boolean logic equations for a one-bit full-adder. Use the display system task to output the result to the console. Experiment with using X input values as inputs to these logic expressions.

Multi-bit logic types are used for modeling bit vectors. Figure 3 shows an example program that illustrates multi-bit logic types. Create a new Verilog source file named utb\_logic-mbit.v and copy some or all of this code. Compile this source file and run the resulting simulator.

Lines 5–8 declares multi-bit logic variables. The square brackets contain the index of the most-significant and the least-significant bit. In this course, you should always use zero as the index of the least significant bit. Note that to declare a four-bit logic value, we use [3:0] not [4:0].

Lines 14–17 illustrate multi-bit literals that can be used to declare constant values. These literals have the following general syntax: <bitwidth>'<base><number> where <base> can be b for binary, h for hexadecimal, or d for decimal. It is legal to include underscores in the literal, which can be helpful for improving the readability of long literals.

Lines 24–28 illustrate multi-bit versions of the basic bitwise logic operators. As before, we should always ask ourselves, "What will happen if one of the inputs is an X?" Lines 35–39 illustrate what happens if two bits in the second value are Xs. Note that some bits in the result are X and some can be guaranteed to be either a 0 or 1.

Lines 45–50 illustrate the reduction operators. These operators take a multi-bit logic value and combine all of the bits into a single-bit value. For example, the OR reduction operator (|) will OR all of the bits together.

★ *To-Do On Your Own:* We will use relational operators (e.g., ==) to compare two multi-bit logic values, but see if you can achieve the same effect with the bitwise XOR/XNOR operators and OR/NOR reduction operators.

```

1 `include "vc/trace.v"

module top( input logic clk, input logic linetrace );

3

// Declare multi-bit logic variables

5

logic [ 3:0] A; // 4-bit logic variable

logic [ 3:0] B; // 4-bit logic variable

logic [ 3:0] C; // 4-bit logic variable

logic [11:0] D; // 12-bit logic variable

10

11

initial begin

12

// Multi-bit literals

14

15

A = 4'b0101;

display( "4'b0101 = %x", A );

16

D = 12'b1100_1010_0101; $display( "12'b1100_1010_0101 = %x", D );

17

D = 12'hca5; $display("12'hca5 = %x", D);

D = 12'd1058; $display("12'd1058 = %x", D);

18

19

20

// Bitwise logical operators for doing AND, OR, XOR, and NOT

21

22

A = 4'b0101;

23

24

B = 4'b0011;

25

C = A \& B; $display( "4'b0101 & 4'b0011 = %b", C);

C = A \mid B; $display( "4'b0101 | 4'b0011 = %b", C);

27

28

29

30

// Bitwise logical operators when some bits are X

32

A = 4'b0101;

34

35

B = 4'b00xx;

36

display( "4'b0101 & 4'b00xx = %b", C );

C = A \& B;

37

C = A \mid B; $display( "4'b0101 | 4'b00xx = %b", C);

38

C = A ^ B; $display( "4'b0101 ^ 4'b00xx - %b", C );

C = A ^ B; $display( "4'b0101 ^ 4'b00xx = %b", C );

C = B; $display( "4'b00xx = %b", C );

39

40

41

// Reduction operators

43

44

45

A = 4'b0101;

46

47

48

49

50

51

52

53

54

$finish();

55

57

endmodule

```

Code at tut4-verilog/utb\_ex-basics-logic-mbit.v

**Figure 3: Verilog Basics: Multi-Bit Logic and Logical Operators –** Experimenting with multi-bit logic variables and literals, bitwise logical operators, and reduction operators.

### 3.3. Shift Operators

Figure 4 illustrates three shift operators on multi-bit logic values. Create a new Verilog source file named utb\_logic-shift.v and copy some or all of this code. Compile this source file and run the resulting simulator.

Notice how the logical shift operators (<<, >>) always shift in zeros, but the arithmetic right shift operator (>>>) replicates the most-significant bit. Verilog requires that the left-hand operand to the arithmetic shift operator be explicitly denoted as signed, which we have done using the signed system task. We recommend this approach and avoiding the use of signed data types.

★ *To-Do On Your Own:* Experiment different multi-bit logic values and shift amounts.

```

1 `include "vc/trace.v"

3 module top ( input logic clk, input logic linetrace );

4

logic [7:0] A;

logic [7:0] B;

logic [7:0] C;

initial begin

// Fixed shift amount for logical shifts

11

12

A = 8'b1110_0101;

13

14

$display( "8'bl110_0101 << 2 = %b", C );

$display( "8'b1110_0101 << 2 = %b", C );

C = A \ll 1;

$display( "8'b1110_0101 << 1 = %b", C );

15

C = A << 2;

16

$display( "8'b1110_0101 << 3 = %b", C );

C = A << 3;

17

18

$display( "8'b1110_0101 >> 1 = %b", C );

19

C = A \gg 1;

$display( "8'b1110_0101 >> 2 = %b", C);

C = A \gg 2;

20

C = A >> 3;

$display( "8'b1110_0101 >> 3 = %b", C );

22

23

// Fixed shift amount for arithmetic shifts

24

A = 8'b0110_0100;

25

26

C = $signed(A) >>> 1; $display( "8'b0110_0100 >>> 1 = %b", C );

27

C = $signed(A) >>> 2; $display( "8'b0110_0100 >>> 2 = %b", C );

C = $signed(A) >>> 3; $display( "8'b0110_0100 >>> 3 = %b", C);

29

A = 8'b1110_0101;

31

33

34

C = $signed(A) >>> 3; $display( "8'b1110_0101 >>> 3 = %b", C);

36

37

// Variable shift amount for logical shifts

38

A = 8'b1110_0101;

B = 8'd2;

40

41

C = A \ll B;

display("8'b1110_0101 << 2 = \%b", C);

42

$display( "8'b1110_0101 >> 2 = %b", C);

C = A \gg B;

43

$finish();

45

end

47

49 endmodule

```

Code at tut4\_verilog/utb\_ex-basics-logic-shift.v

**Figure 4: Verilog Basics: Shift Operators –** Experimenting with logical and arithmetic shift operators and fixed/variable shift amounts.

### 3.4. Arithmetic Operators

Figure 5 illustrates the addition and subtraction operators for multi-bit logic values. Create a new Verilog source file named utb\_logic-arith.v and copy some or all of this code. Compile this source file and run the resulting simulator.

These operators treat the multi-bit logic values as unsigned integers. Although Verilog does include support for signed arithmetic, these constructs may not be synthesizable so you are required to use only unsigned arithmetic. Also recall that \*, /, %, \*\* are not allowed in the synthesizable portion of your design.

Note that carefully considering the bitwidths of the input and output variables is important. Lines 22–23 illustrate overflow and underflow. You can see that if you overflow the bitwidth of the output variable then the result will simply wrap around. Similarly, since we are using unsigned arithmetic negative numbers wrap around. This is also called modular arithmetic.

★ To-Do On Your Own: Try writing some code which does a sequence of additions resulting in overflow and then a sequence of subtractions that essentially undo the overflow. For example, try 200 + 400 + 400 - 400 - 400. Does this expression produce the expected answer even though the intermediate values overflowed?

```

`include "vc/trace.v"

1

2 module top ( input logic clk, input logic linetrace );

logic [7:0] A;

4

logic [7:0] B;

logic [7:0] C;

initial begin

// Basic arithmetic with no overflow or underflow

10

11

A = 8'd28:

12

B = 8'd15;

13

C = A + B; $display( "8'd28 + 8'd15 = %d", C);

15

C = A - B; display("8'd28 - 8'd15 = %d", C);

17

// Basic arithmetic with overflow and underflow

A = 8'd250:

20

B = 8'd15;

21

22

C = A + B; $display( "8'd250 + 8'd15 = %d", C);

C = B - A; $display( "8'd15 - 8'd250 = %d", C);

24

$finish();

26

27

28

29

endmodule

```

Code at tut4\_verilog/utb\_ex-basics-logic-arith.v

**Figure 5: Verilog Basics: Arithmetic Operators –** Experimenting with arithmetic operators for addition and subtraction.

### 3.5. Relational Operators

Figure 6 illustrates the relational operators used for comparing two multi-bit logic values. Create a new Verilog source file named utb\_logic-relop.v and copy some or all of this code. Compile this source file and run the resulting simulator.

Lines 28–33 illustrate what happens if some of the bits are Xs for these relational operators. Notice that we can still determine two values are not equal even if some bits are unknown. If the bits we do know are different then the unknown bits do not matter; we can guarantee that the full bit vectors are not equal. So in this example, since we know that the top-two bits in 4'b1100 and 4'b10xx then we can guarantee that the two values are not equal even though the bottom two bits of one operand are unknown.

The <, >, <=, >= operators behave slightly differently than the == and != operators when considering values with Xs. In this example, we should be able to guarantee that 4'b1100 is always greater than 4'b10xx (assuming these are unsigned values), since no matter what the bottom two bits are in the second operand it cannot be greater than the first operand. However, if you run this simulation, then you will see that the result is still X. This is not a bug and is correct according to the Verilog language specification. This is a great example of how Verilog has relatively complicated and sometimes inconsistent language semantics. Originally, there was no Verilog standard. The most common Verilog simulator was the de-factor language standard. I imagine the reason there is this difference between how == and < handle X values is simply because in the very first Verilog simulators it was the most efficient solution. These kind of "simulator implementation issues" can be found throughout the Verilog standard.

Lines 40–43 illustrates signed comparisons using the signed system task to to interpret the unsigned input operands as signed values. To simplify our designs, we do not allow students to use signed types. We should explicitly use the signed system task whenever we need to ensure signed comparisons.

★ *To-Do On Your Own:* Try composing relational operators with the boolean logic operators we learned about earlier in this section to create more complicated expressions.

```

1 `include "vc/trace.v"

3 module top ( input logic clk, input logic linetrace );

// Declare multi-bit logic variables

a; // 1-bit logic variable

logic [ 3:0] A; // 4-bit logic variable

logic [ 3:0] B; // 4-bit logic variable

10

11

initial begin

12

13

// Relational operators

14

A = 4'd15; B = 4'd09;

15

16

a = (A == B); $display("(15 == 9) = %x", a);

17

a = ( A != B );  $display( "(15 != 9) = %x", a );

18

a = ( A > B ); $display("(15 > 9) = %x", a );

a = (A >= B);  $display( "(15 >= 9) = %x", a);

a = (A < B);  $display( "(15 < 9) = %x", a);

20

21

a = (A \le B); $display("(15 <= 9) = \%x", a);

22

23

// Relational operators when some bits are X

24

25

A = 4'b1100; B = 4'b10xx;

27

a = (A == B); $display("(4'b1100 == 4'b10xx) = %x", a);

28

a = ( A != B );  $display( "(4'b1100 != 4'b10xx) = %x", a );

29

a = (A > B); $display( "(4'b1100 > 4'b10xx) = %x", a);

31

a = (A < B); $\(\frac{1}{2}\text{display}(\(\frac{1}{2}\text{b1100} < \frac{4}{2}\text{b10xx}) = \(\frac{1}{2}\text{x}\), a);

32

// Signed relational operators

33

34

A = 4'b1111; // -1 in twos complement

B = 4'd0001; // 1 in twos complement

36

A >

a = (

38

39

a = (

a = ( $signed(A) > $signed(B) ); $display( "(-1 > 1) = \%x", a );

40

a = ( $signed(A) < $signed(B) ); $display( "(-1 < 1) = \%x", a );

41

$finish():

43

44

end

45

47 endmodule

```

Code at tut4\_verilog/utb\_ex-basics-logic-relop.v

**Figure 6: Verilog Basics: Relational Operators –** Experimenting with relational operators.

#### 3.6. Concatenation Operators

Figure 7 illustrates the concatenation operators used for creating larger bit vectors from multiple smaller bit vectors. Create a new Verilog source file named utb\_logic-concat.v and copy some or all of this code. Compile this source file and run the resulting simulator.

Lines 18–20 illustrate concatenating three four-bit logic variables and then assigning the result to a 12-bit logic variable. Lines 25–26 illustrate concatenating a four-bit logic variable with an eight-bit logic variable. The repeat operator can be used to duplicate a given logic variable multiple times when creating larger bit vectors. On Line 33, we replicate a four-bit logic value three times to create a 12-bit logic value.

★ *To-Do On Your Own:* Experiment with different variations of concatenation and the repeat operator to create interesting bit patterns.

```

`include "vc/trace.v"

2 module top( input logic clk, input logic linetrace );

logic [ 3:0] A; // 4-bit logic variable

logic [ 3:0] B; // 4-bit logic variable

logic [ 3:0] C; // 4-bit logic variable

logic [ 7:0] D; // 18-bit logic variable

logic [11:0] E; // 12-bit logic variable

initial begin

11

// Basic concatenation

12

13

A = 4'ha;

B = 4'hb;

15

C = 4'hc;

16

D = 8'hde;

17

18

19

20

E = \{ B, C, A \};  $display( "{ 4'hb, 4'hc, 4'ha } = %x", E );

21

22

$display( "{ 4'ha, 8'hde } = %x", E );

$display( "{ 8'hde 4'ha l - %y" E }.

E = \{ A, D \};

23

E = { D, A };

$display( "{ 8'hde, 4'ha } = %x", E );

24

25

E = \{ A, 8'hf0 \};  $display( "{ 4'ha, 8'hf0 } = %x", E ); E = \{ 8'hf0, A \};  $display( "{ 8'hf0, 4'ha } = %x", E );

26

27

28

// Repeat operator

29

A = 4'ha;

31

B = 4'hb;

33

$display( "{ 4'ha, 4'ha, 4'ha } = %x", E );

E = \{ 3\{A\} \};

E = \{ A, \{2\{B\}\} \}; \text{ $display}( "{ 4'ha, 4'hb, 4'hb } = %x", E );

35

$finish();

36

37

end

39 endmodule

```

Code at tut4\_verilog/utb\_ex-basics-logic-concat.v

**Figure 7: Verilog Basics: Concatenation Operators –** Experimenting with the basic concatenation operator and the repeat operator.

### 3.7. Enum Data Types

The logic data type will be the most common data type we use in our synthesizable RTL since a logic variable has a direct one-to-one correspondence with a bit vector in hardware. However, there are certain cases where using a logic variable can be quite tedious and error prone. SystemVerilog has introduced two new kinds of user-defined types that can greatly simplify some portions of our designs. In this subsection, we introduce the enum type which enables declaring variables that can only take on a predefined list of labels.

Figure 8 illustrates creating and using an enum type for holding a state variable which can take on one of four labels. Create a new Verilog source file named utb\_enum.v and copy all of this code. Compile this source file and run the resulting simulator.

Lines 3–8 declare a new enum type named state\_t. Note that state\_t is not a new *variable* but is instead a new *type*. We will use the \_t suffix to distinguish type names from variable names. Note that after the enum keyword we have included a *base type* of logic [\$clog2(4)-1:0]. This base type specifies how we wish variables of this new type to be stored. In this case, we are specifying that state\_t variables should be encoded as a two-bit logic value. The clog2 system task calculates the number of bits in the given argument; it is very useful when writing more parameterized code. So in this situation we just need to pass in the number of labels in the enum to clog2. SystemVerilog actually provides many different ways to create enum types including anonymous types, types where we do not specify the base type, or types where we explicitly define the value for each label. In this course, you should limit yourself to the exact syntax shown in this example.

Line 14 declares a new variable of type state\_t. This is the first time we have seen a variable which has a type other than logic. The ability to introduce new user-defined types is one of the more powerful features of SystemVerilog. Lines 21–24 sets the state variable using the labels declared as part of the new state\_t type. Lines 28–40 compare the value of the state variable with these same labels, and these comparisons can be used to take different action based on the current value.

There are several advantages to using an enum type compared to the basic logic type to represent a variable that can hold one of several labels including: (1) more directly capturing the designer's intent to improve code quality; (2) preventing mistakes by eliminating the possibility of defining labels with the same value or defining label values that are too large to fit in the underlying storage; and (3) preventing mistakes when assigning variables of a different type to an enum variable.

★ To-Do On Your Own: Create your own new enum type for the state variable we will use in the GCD example later in this tutorial. The new enum type should be called state\_t and it should support three different labels: STATE\_IDLE, STATE\_CALC, STATE\_DONE. Write some code to set and compare the value of a corresponding state variable.

```

`include "vc/trace.v"

1

3 // Declare enum type

5 typedef enum logic [$clog2(4)-1:0] {

STATE_A,

STATE_B,

STATE_C,

STATE_D

10 } state_t;

11

12 module top ( input logic clk, input logic linetrace );

// Declare variables

14

15

state_t state;

logic result;

17

initial begin

19

// Enum lable literals

21

22

state = STATE_A; $display( "STATE_A = %d", state );

23

state = STATE_B; $display( "STATE_B = %d", state );

24

state = STATE_C; $display( "STATE_C = %d", state );

state = STATE_D; $display( "STATE_D = %d", state );

26

// Comparisons

28

state = STATE_A;

30

31

result = ( state == STATE_A );

32

$display( "( STATE_A == STATE_A ) = %x", result );

33

result = ( state == STATE_B );

35

$display( "( STATE_A == STATE_B ) = %x", result );

37

result = ( state != STATE_A );

$display( "( STATE_A != STATE_A ) = %x", result );

result = ( state != STATE_B );

41

$display( "( STATE_A != STATE_B ) = %x", result );

42

43

44

end

46 endmodule

```

Code at tut4\_verilog/utb\_ex-basics-enum.v

**Figure 8: Verilog Basics: Enum Data Types –** Experimenting with enum data types including setting the value of an enum using a label and using the equality operator.

### 3.8. Struct Data Types

User-defined structures are now supported in SystemVerilog. Figure 9 illustrates creating and using a struct type for holding a variable with predefined named bit fields. Create a new Verilog source file named utb\_struct.v and copy all of this code. Compile this source file and run the resulting simulator.

Lines 3–7 declare a new struct type named point\_t. Again note that point\_t is not a new *variable* but is instead a new type. As before we use the \_t suffix to distinguish type names from variable names. Note that after the struct keyword we have included the packed keyword which specifies that variables of this type should have an equivalent underlying logic storage. SystemVerilog also includes support for unpacked structs, but in this course, you should limit yourself to the exact syntax shown in this example. In addition to declaring the name of the new struct type, we also declare the named bit fields within the new struct type. The order of these bit fields is important; the first field will go in the most significant position of the underlying logic storage, the second field will go in the next position, and so on.

Lines 13–14 declare two new variables of type point\_t. Line 18 declares a new logic variable with a bitwidth large enough to hold a variable of type point\_t. We can use the bits system task to easily determine the total number of bits required to store a struct type. Lines 24–26 set the three fields of the point variable and Lines 28–30 read these three fields in order to display them. Line 34 copies one point variable into another point variable. Line 42 and 49 illustrate how to convert a point variable to/from a basic logic variable.

There are several advantages to using a struct type compared to the basic logic type to represent a variable with a predefined set of named bit fields including: (1) more directly capturing the designer's intent to improve code quality; (2) reducing the syntactic overhead of managing bit fields; and (3) preventing mistakes in modifying bit fields and in accessing bit fields.

★ To-Do On Your Own: Create a new struct type for holding the an RGB color pixel. The struct should include three fields named red, green, and blue. Each field should be eight bits. Experiment with reading and writing these named fields.

### 3.9. Ternary Operator

Figure 10 illustrates using the ternary operator for conditional execution. Create a new Verilog source file named utb\_ternary.v and copy some or all of this code. Compile this source file and run the resulting simulator.

Lines 12–19 illustrate using the ternary operator to choose what value to assign to the logic variable c. We can nest multiple ternary operators to compactly create expressions with multiple conditions. Lines 23–31 illustrate using four levels of nesting to choose among four different values for assigning c.

Lines 35–53 illustrate how the ternary operator functions if the conditional is unknown. In lines 35–43, all bits of the conditional are unknown, while in lines 45–53 only one bit of the conditional is unknown. If you examine the output from this simulator, you will see that Verilog semantics require any bits which can be guaranteed to be either 0 or 1 to be set as such, while the remaining bits are set to X. Regardless of the condition, the upper five bits of c are guaranteed to be 00001.

Note that the four ternary operators cover all possible combinations of the two-bit input, so the final value (i.e., 8'h0e) will never be used. In other words, if the conditionals contain unknowns this does *not* mean the condition evaluates to false. This is very different from the if statements described in the next subsection.

Aside: For some reason, many students insist on writing code like this:

```

a = ( cond_a ) ? 1'b1 : 1'b0;

b = ( cond_b ) ? 1'b0 : 1'b1;

```

This obfuscates the code and is not necessary. We are using a ternary operator to simply choose between 0 or 1. You should just assign the result of the conditional expression to a and b like this:

```

a = ( cond_a );

b = !( cond_b );

```

★ *To-Do On Your Own:* Experiment with different uses of the ternary operator.

```

`include "vc/trace.v"

module top ( input logic clk, input logic linetrace );

logic [7:0] a;

5

logic [7:0] b;

logic [7:0] c;

7

logic [1:0] sel;

initial begin

10

11

// ternary statement

12

a = 8'd30;

14

15

b = 8'd16;

16

c = (a < b) ? 15 : 14;

17

$display( "c = %d", c );

18

19

c = (b < a) ? 15 : 14;

20

$display( "c = %d", c );

21

// nested ternary statement

23

25

sel = 2'b01;

c = (sel == 2'b00)?8'h0a

27

: ( sel == 2'b01 ) ? 8'h0b

28

: ( sel == 2'b10 ) ? 8'h0c

29

: ( sel == 2'b11 ) ? 8'h0d

30

8'h0e:

32

$display( "sel = 1, c = %b", c );

33

34

// nested ternary statement w/ X

36

sel = 2'bxx;

37

38

c = (sel == 2'b00) ? 8'h0a

39

: ( sel == 2'b01 ) ? 8'h0b

40

: ( sel == 2'b10 ) ? 8'h0c

41

: ( sel == 2'b11 ) ? 8'h0d

43

44

display("sel = x, c = \%b", c);

45

sel = 2'bx0;

c = (sel == 2'b00) ? 8'h0a

: ( sel == 2'b01 ) ? 8'h0b

50

51

: ( sel == 2'b10 ) ? 8'h0c

: ( sel == 2'b11 ) ? 8'h0d

52

53

54

display("sel = x, c = \%b", c);

55

$finish();

57

58

end

59

endmodule

61

Code at

tut4_verilog/utb_ex-basics-ternary.v

```

Figure 10: Verilog Basics: Ternary Operator – Experimenting with the ternary operator including nested statements and what happens if the conditional includes an unknown.

```

1 `include "vc/trace.v"

// Declare struct type

typedef struct packed { // Packed format:

logic [3:0] x; // 11 8 7 4 3 0

// +---+

logic [3:0] y;

// | x | y | z |

// +---+

logic [3:0] z;

10 } point_t;

12 module top ( input logic clk, input logic linetrace );

13

// Declare variables

14

15

16

point_t point_a;

point_t point_b;

17

// Declare other variables using $bits()

19

logic [$bits(point_t)-1:0] point_bits;

21

22

initial begin

23

24

// Reading and writing fields

25

26

point_a.x = 4'h3;

27

point_a.y = 4'h4;

28

point_a.z = 4'h5;

30

31

$display( "point_a.x = %x", point_a.x );

$display( "point_a.y = %x", point_a.y );

32

$display( "point_a.z = %x", point_a.z );

33

34

// Assign structs

35

point_b = point_a;

37

$display( "point_b.x = %x", point_b.x );

39

$display( "point_b.y = %x", point_b.y );

$display( "point_b.z = %x", point_b.z );

41

42

// Assign structs to bit vector

43

44

45

point_bits = point_a;

46

$display( "point_bits = %x", point_bits );

48

// Assign bit vector to struct

49

50

point_bits = { 4'd13, 4'd9, 4'd3 };

51

52

point_a = point_bits;

53

$display( "point_a.x = %x", point_a.x );

$display( "point_a.y = %x", point_a.y );

$display( "point_a.z = %x", point_a.z );

55

57

58

$finish();

59

end

61 endmodule

```

Code at tut4\_verilog/utb\_ex-basics-struct.v

**Figure 9: Verilog Basics: Struct Data Types –** Experimenting with struct data types including read/writing fields and converting to/from logic bit vectors.

#### 3.10. If Statements

Figure 11 illustrates using if statements. Create a new Verilog source file named utb\_if.v and copy some or all of this code. Compile this source file and run the resulting simulator.

The if statement resembles similar constructs in many other programming languages. Lines 11–20 illustrate basic if statements and lines 24–33 illustrate if/else statements.

There are some subtle issues involved in how an if statement handles X values in the conditional. Lines 37–46 illustrate this issue. The sel value in this example is a single-bit X. What would we expect the value of a to be after this if statement? Since the conditional is unknown, we might expect any variables that are written from within the if statement to also be unknown. In other words, we might expect the value of a to be X after this if statement. If you run this example code, you will see that the value of a is actually 8'h0b. This means that an X value in the conditional for an if statement is not treated as unknown but is instead simply treated as if the conditional evaluated to false! This issue is called *X optimism* since unknowns are essentially optimistically turned into known values. X optimism can cause subtle simulation/synthesis mismatch issues. If you are interested, there are several resources on the public course webpage that go into much more detail. For this course, we don't need to worry too much about X optimism since we are not actually synthesizing our designs.

★ *To-Do On Your Own:* Experiment with different if statements including nested if statements. Experiment with what happens when the conditional is unknown.

```

module top ( input logic clk, input logic linetrace );

logic [7:0] a;

3

logic [7:0] b;

logic

5

sel;

initial begin

// if statement

10

a = 8'd30;

11

b = 8'd16;

12

13

if (a == b) begin

14

$display( "30 == 16" );

15

16

17

if ( a != b ) begin

18

$display( "30 != 16" );

19

20

21

// if else statement

23

sel = 1'b1:

25

if ( sel == 1'b0 ) begin

26

a = 8'h0a;

27

28

end

29

else begin

a = 8'h0b:

30

32

$display( "sel = 1, a = %x ", a );

33

34

// if else statement w/ X

36

sel = 1'bx;

37

38

if ( sel == 1'b0 ) begin

39

40

a = 8'h0a;

end

41

else begin

a = 8'h0b;

43

44

45

display("sel = x, a = %x", a);

46

47

48

end

endmodule

```

Code at tut4\_verilog/utb\_ex-basics-if.v

Figure 11: Verilog Basics: If Statements – Experimenting with if statements including what happens if the conditional includes an unknown.

#### 3.11. Case Statements

Figure 12 illustrates using case statements. Create a new Verilog source file named utb\_case.v and copy some or all of this code. Compile this source file and run the resulting simulator.

The case statement resembles similar constructs in many other programming languages. Lines 12–22 illustrate a basic case statement where a two-bit sel variable is used to choose one of four case items.

There are similar issues as with the if statement in terms of how case statements handle X values in the conditional. In lines 26–36, the sel variable is set to all Xs. We might expect since the input to the case statement is unknown the output should also be unknown. However, if we look at the value of a after executing this case statement it will be 8'h0e. In other words, if there is an X in the input to the case statement, then the case statement will fall through to the default case. In order to avoid X optimism, we recommend students always include a default case that sets all of the output variables to Xs.

Notice that it is valid syntax to use X values in the case items, as shown on lines 48–49. These will actually match Xs in the input condition, which is almost certainly not what you want. This does not model any kind of real hardware; we cannot check for Xs in hardware since in real hardware an unknown must be known (i.e., all Xs will either be a 0 or a 1 in real hardware). Given this, you should never use Xs in the case items for a case statement.

To-Do On Your Own: Experiment with a larger case statement for a sel variable with three instead of two bits.

```

`include "vc/trace.v"

module top( input logic clk, input logic linetrace );

// Declaring Variables

logic [1:0] sel;

logic [7:0] a;

7

initial begin

10

// case statement

11

12

sel = 2'b01:

14

15

case ( sel )

2'b00 : a = 8'h0a;

16

2'b01 : a = 8'h0b;

17

2'b10 : a = 8'h0c;

2'b11 : a = 8'h0d;

18

19

default : a = 8'h0e;

20

21

22

display("sel = 01, a = %x", a);

23

25

// case statement w/ X

26

27

sel = 2'bxx;

28

case ( sel )

29

2'b00 : a = 8'h0a;

30

2'b01 : a = 8'h0b;

2'b10 : a = 8'h0c;

2'b11 : a = 8'h0d;

32

33

default : a = 8'h0e;

34

35

endcase

36

display("sel = xx, a = %x", a);

37

38

39

// Do not use x's in the case

40

// selection items

41

sel = 2'bx0;

43

44

case ( sel )

45

2'b00 : a = 8'h0a;

2'b01 : a = 8'h0b;

46

2'b10

: a = 8'h0c;

47

2'b11 : a = 8'h0d:

48

2'bx0 : a = 8'h0e;

49

2'bxx : a = 8'h0f;

50

default : a = 8'h00;

51

endcase

52

display("sel = x0, a = %x", a);

55

57

endmodule

```

Code at tut4\_verilog/utb\_ex-basics-case.v

Figure 12: Verilog Basics: Case Statements – Experimenting with case statements including what happens if the selection expression and/or the case expressions includes an unknown.

#### 3.12. Casez Statements

Figure 13 illustrates using casez statements. Create a new Verilog source file named utb\_casez.v and copy some or all of this code. Compile this source file and run the resulting simulator.

The casez statement is very different from what you might find in other programming languages. The casez statement is a powerful construct that can enable very concise hardware models, but must be used carefully. A casez statement enables a designer to do "wildcard" matching on the input variable. Lines 10-23 illustrate using a casez statement to implement a "leading-one detector". This kind of logic outputs the bit position of the leastsignificant one in the input variable. We can use ? characters in the case items as wildcards that will match either a 0 or 1 in the input variable. So both 4'b0100 and 4'b1100 will match the fourth case item. Implementing similar functionality using a case statement would require 16 items. Besides being more verbose, using a case statement also opens up additional opportunities for errors.

A casez statement behaves similarly to a case statement when there are Xs in the input. Lines 27–40 illustrate a situation where two of the bits in the input variable are unknown. This will match the default case and the output will be Xs.

Aside: Verilog includes a casex statement which you should never use. The reasoning is rather subtle, but to be safe stick to using casez statement if you need wildcard matching (and *only* if you need wildcard matching).

★ To-Do On Your Own: Experiment with a larger casez statement to implement a leading-one detector for an input variable with eight instead of four bits. How many case items would we need if we used a case statement to implement the same functionality?

```

`include "vc/trace.v"

module top( input logic clk, input logic linetrace );

logic [3:0] a;

logic [7:0] b;

initial begin

// casez statement

10

a = 4'b0100;

11

12

casez (a)

14

4'b0000 : b = 8'd0;

15

4'b???1 : b = 8'd1;

16

4'b??10 : b = 8'd2;

17

4'b?100 : b = 8'd3;

18

4'b1000 : b = 8'd4;

19

default : b = 8'hxx:

21

endcase

23

display( "a = 4'b0100, b = %x", b );

25

// casez statement w/ Xs

a = 4'b01xx:

29

casez (a)

30

4'b0000 : b = 8'd0;

32

33

4'b???1 : b = 8'd1:

4'b??10 : b = 8'd2;

34

4'b?100 : b = 8'd3;

4'b1000 : b = 8'd4;

36

37

default : b = 8'hxx;

38

39

endcase

40

display( "a = 4'b01xx, b = %x", b );

41

43

44

endmodule

```

Code at tut4\_verilog/utb\_ex-basics-casez.v

Figure 13: Verilog Basics: Casez Statements – Experimenting with casez statements to illustrate their use as priority selectors with wild-cards.

# 4. Registered Incrementer

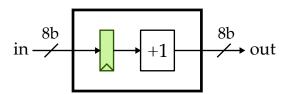

In this section, we will create our very first Verilog hardware model and learn how to test this module using waveforms, ad-hoc testing, and a simple unit testing framework. It is good design practice to usually draw some kind of diagram of the hardware we wish to model before starting to develop the corresponding Verilog model. This diagram might be a block-level diagram, a datapath diagram, a

**Figure 14: Block Diagram for Registered Incrementer** – An eight-bit registered incrementer with an eight-bit input port, an eight-bit output port, and an (implicit) clock input.

finite-state-machine diagram, or even a control signal table; the more we can structure our Verilog code to match this diagram the more confident we can be that our model actually models what we think it does. In this section, we wish to model the eight-bit registered incrementer shown in Figure 14.

#### 4.1. RTL Model of Registered Incrementer

Figure 16 shows the Verilog code which corresponds to the diagram in Figure 14. Every Verilog file should begin with a header comment as shown on lines 1–9 in Figure 16. The header comment should identify the primary module in the file, and include a brief description of what the module does. Reserve discussion of the actual implementation for later in the file. In general, you should attempt to keep lines in your Verilog source code to less than 74 characters. This will make your code easier to read, enable printing on standard sized paper, and facilitate viewing two source files side-by-side on a single monitor. Note that the code in Figure 16 is artificially narrow so we can display two code listings side-by-side. Lines 11–12 create an "include guard" using the Verilog pre-processor. An include guard ensures that even if we include this Verilog file multiple times the modules within the file will only be declared once. Without include guards, the Verilog compiler will likely complain that the same module has been declared multiple times. Make sure that you have the corresponding end of the include guard at the bottom of your Verilog source file as shown on line 43.

Verilog does not have a clean way to manage namespaces for macros and module names. This means that if you use the same macro or module name in two different files it will create a namespace collision which can potentially be very difficult to debug. We will follow very specific naming conventions to eliminate any possibility of a namespace collision. Our convention will to use the subdirectory path as a prefix for all Verilog macro and module names. Since the registered incrementer is in the directory tut4\_verilog/regincr, we will use TUT4\_VERILOG\_REGINCR\_ as a prefix for all macro names and tut4\_verilog\_regincr\_ as a prefix for all module names. You can see this prefix being used for the macros on lines 11–12 and for the module name on line 14. To reiterate, Verilog macro and module name must use the subdirectory path as a prefix. While a bit tedious, this is essential to avoiding namespace collisions.

As always, we begin by identifying the module's interface which in this case will include an eightbit input port, eight-bit output port, and a clock input. Lines 15–20 in Figure 16 illustrate how we represent this interface using Verilog. A common mistake is to forget the semicolon (;) on line 20. A couple of comments about the coding conventions that we will be using in this course. All module names should always include the subproject name as a prefix (e.g., ex\_regincr\_). The portion of the name after this prefix should usually use CamelCaseNaming; each word begins with a capital letter without any underscores (e.g., RegIncr). Port names (as well as variable and module instance names) should use underscore\_naming; all lowercase with underscores to separate words. As shown on lines 16–19, ports should be listed one per line with a two space initial indentation. The bitwidth specifiers and port names should all line up vertically. As shown on lines 15 and 20, the opening and closing parenthesis should be on their own separate lines. Carefully group ports to help the reader understand how these ports are related. Use port names (as well as variable and module instance

```

1 //======

// Registered Incrementer

// Registered Incrementer

// Registered Incrementer

// This is a simple example of a module

// This is a simple example of a module

// This is a simple example of a module

// This is a simple example of a module

// This is a simple example of a module

// Tora registered incrementer which

// combines a positive edge triggered

// register with a combinational +1

// register with a combinational +1

// incrementer. We use flat register

// transfer-level modeling.

// transfer-level modeling.

10

11 `ifndef TUT4_VERILOG_REGINCR_REG_INCR_V 11 `ifndef TUT4_VERILOG_REGINCR_REG_INCR_V 12 `define TUT4_VERILOG_REGINCR_REG_INCR_V 12 `define TUT4_VERILOG_REGINCR_REG_INCR_V

module tut4_verilog_regincr_RegIncr

14 module tut4_verilog_regincr_RegIncr

14

clk,

clk,

input logic

16

17

input

input

16

17

input logic

reset,

reset,

18

input logic [7:0] in,

input [7:0] in,

18

19

output logic [7:0] out

output [7:0] out

19

20

20

21

21

// Sequential logic

// Sequential logic

22

23

23

24

logic [7:0] reg_out;

24

reg [7:0] reg_out;

always_ff @( posedge clk ) begin

always @( posedge clk ) begin

25

25

if ( reset )

if ( reset )

reg_out <= '0;

27

reg_out <= 0;

27

28

else

28

else

reg_out <= in;

reg_out <= in;

30

30

31

31

// Combinational logic

// Combinational logic

32

32

reg [7:0] temp_wire;

logic [7:0] temp_wire;

34

34

always_comb begin

35

always Q(*) begin

35

temp_wire = reg_out + 1;

temp_wire = reg_out + 1;

36

37

37

38

38

assign out = temp_wire;

39

39

assign out = temp_wire;

endmodule

41 endmodule

41

42

`endif /* TUT4_VERILOG_REGINCR_REG_INCR_V */

`endif /* TUT4_VERILOG_REGINCR_REG_INCR_V */

Code at regincr/ex-regincr-RegIncr.sv

Code at regincr/ex-regincr-RegIncr.v

```

**Figure 15: Registered Incrementer** – An eightbit registered +1 incrementer corresponding to the diagram in Figure 14.

**Figure 16: Registered Incrementer** – An eightbit registered +1 incrementer using Verilog-2001 constructs.

names) that are descriptive; prefer longer descriptive names (e.g., write\_en) over shorter confusing names (e.g., wen).

Lines 22–39 model the internal behavior of the module. We usually prefer using two spaces for each level of indentation; larger indentation can quickly result in significantly wasted horizontal space. You should always use spaces and never insert any real tab characters into your source code. You must limit yourself to synthesizable RTL for modeling your design. We will exclusively use two kinds of always blocks: always\_ff concurrent blocks to model sequential logic and always\_comb concurrent blocks to model combinational logic We require students to clearly distinguishing between the portions of your code that are meant to model sequential logic from those portions meant to model combinational logic. This simple guideline can save significant frustration by making it easy to see subtle errors. For example, by convention we should only use non-blocking assignments in sequential logic

(e.g., the <= operator on line 27) and we should only use blocking assignments in combinational logic (e.g., the = operator on line 36). We use the variable reg\_out to hold the intermediate value between the register and the incrementer, and we use the variable temp\_wire to hold the intermediate value between the incrementer and the output port. reg\_out is modeling a register while temp\_wire is modeling a wire. Notice that both of these variables use the logic data type; what makes one model a register while the other models a wire is how these variables are used. The sequential concurrent block update to reg\_out means it models a register. The combinational concurrent block update to temp\_wire means it models a wire.

The register incrementer illustrates the two fundamental ways to model combinational logic. We have used an always\_comb concurrent block to model the actual incrementer logic and a continuous assignment statement (i.e., assign) to model connecting the temporary wire to the output port. We could just have easily written logic as part of the assign statement. For example, we could have used assign out = reg\_out + 1 and skipped the always\_comb concurrent block. In general, we prefer continuous assignment statements over always @(\*) concurrent blocks to model combinational logic, since it is easier to model less-realistic hardware using always\_comb concurrent blocks. There is usually a more direct one-to-one mapping from continuous assignment statements to real hardware. However, there are many cases where it is significantly more convenient to use always\_comb concurrent blocks or just not possible to use continuous assignment statements. Students will need to use their judgment to determine the most elegant way to represent the hardware they are modeling while still ensuring there is a clear mapping from the model to the target hardware.

Figure 15 illustrates a few new SystemVerilog constructs. Figure 16 illustrates the exact same registered incrementer implemented using the older Verilog-2001 hardware description language. Verilog-2001 uses reg and wire to specify variables instead of logic. All ports are of type wire by default. Determining when to use reg and wire is subtle and error prone. Note that reg is a misnomer; it does *not* model a register! On line 34, we must declare temp\_wire to be of type reg even though it is modeling a wire. Verilog-2001 requires using reg for any variable written by an always concurrent block. Verilog-2001 uses a generic always block for both sequential and combinational concurrent blocks. While the always @(\*) syntax is an improvement over the need in Verilog-1995 to explicitly define sensitivity lists, always\_ff and always\_comb more directly capture designer intent and allow automated tools to catch common errors. For example, a Verilog simulator can catch errors where a designer accidentally uses a non-blocking assignment in an always\_comb concurrent block, or where a designer accidentally writes the same logic variable from two different always\_comb concurrent blocks. SystemVerilog is growing in popularity and increasingly becoming the de facto replacement for Verilog-2001, so it is worthwhile to carefully adopt new SystemVerilog features that can improve designer productivity.

Edit the Verilog source file named RegIncr.v in the tut4\_verilog/regincr subdirectory using your favorite text editor. Add the combinational logic shown on lines 34–39 in Figure 16 which models the incrementer logic. We will be using verilator to simulate this registered incrementer module, and verilator does not currently support always\_ff and always\_comb, which is why we are using the Verilog-2001 construct for now.

#### 4.2. Simulating a Model using verilator

```

// Clocking

10

logic clk = 1;

11

always #5 clk = ~clk;

12

// Instaniate the design under test

14

logic

reset = 1;

16

logic [7:0] in;

17

logic [7:0] out;

18

19

tut4_verilog_regincr_RegIncr reg_incr

20

21

.clk (clk),

22

.reset (reset),

23

.in (in),

.out (out)

25

);

// Verify functionality

28

initial begin

30

31

// Dump waveforms

32

33

$dumpfile("regincr-iverilog-sim.vcd");

34

$dumpvars;

35

36

// Reset

37

38

#11;

39

reset = 1'b0;

41

// Test cases

43

in = 8'h00;

44

45

#10;

if ( out != 8'h01 ) begin

46

$display( "ERROR: out, expected = %x, actual = %x", 8'h01, out );

$finish;

47

48

50

in = 8'h13;

51

#10;

52

if ( out != 8'h14 ) begin

53

$display( "ERROR: out, expected = %x, actual = %x", 8'h14, out );

$finish;

54

55

end

57

in = 8'h27;

#10:

59

if ( out != 8'h28 ) begin

$display( "ERROR: out, expected = %x, actual = %x", 8'h28, out );

$finish;

61

62

end

63

$display( "*** PASSED ***" );

65

$finish;

66

end

68

endmodule

```

**Figure 17: Simulator for Registered Incrementer –** A Verilog simulator for the eight-bit registered incrementer in Figure 16.

Now that we have developed a new hardware module, we can test its functionality using a simulation harness. Figure 17 shows an ad-hoc test using non-synthesizable Verilog. Note that we must explicitly include any Verilog files which contain modules that we want to use; Line 5 includes the Verilog source file that contains the registered incrementer. Lines 11–12 setup a clock with a period of 10 time steps. Notice that we are assigning an initial value to the clk net on line 11 and then modifying this net every five timesteps; setting initial values such as this is not synthesizable and should only be used in test harnesses. If you need to set an initial value in your design, you should use properly constructed reset logic.

Lines 19–24 instantiate the device under test. Notice that we use underscore\_naming for the module instance name (e.g., reg\_incr). You should almost always use named port binding (as opposed to positional port binding) to connect nets to the ports in a module instance. Lines 21–23 illustrate the correct coding convention with one port binding per line and the ports/nets vertically aligned. As shown on lines 20 and 24 the opening and closing parenthesis should be on their own separate lines. Although this may seem verbose, this coding style can significantly reduce errors by making it much easier to quickly visualize how ports are connected.

Lines 28–62 illustrate an initial block which executes at the very beginning of the simulation. initial blocks are not synthesizable and should only be used in test harnesses. Lines 32–33 instruct the simulator to dump waveforms for all nets. Line 35 is a delay statement that essentially waits for one timestep. Delay statements are not synthesizable and should only be used in test harnesses. Lines 39–44 implement a test by setting the inputs of the device under test, waiting for 10 time steps, and then checking that the output is as expected. If there is an error, we display an error message and stop the simulation. We include two more tests, and if we make it to the bottom of the initial block then the test has passed.

Edit the Verilog simulation harness named utb\_regincr-iverilog-sim.v in the tut4\_verilog/regincr subdirectory using your favorite text editor. Add the code on lines 20–26 in Figure 17 to instantiate the registered incrementer model. Then use verilator to compile this simulator and run the simulation as follows:

```

% cd ${TUTROOT}

% make regincr/utb_RegIncr.v

```

If everything goes as expected, then the ad-hoc test should display \*\*\* PASSED \*\*\*.

★ To-Do On Your Own: Edit the register incrementer so that it now increments by +2 instead of +1. Use an assign statement instead of the always @(\*) concurrent block to do the incrementer logic. Recompile, rerun the ad-hoc test, and verify that the tests no longer pass. Modify the ad-hoc test so that it includes the correct reference outputs for a +2 incrementer, recompile, rerun the ad-hoc test, and verify that the test now pass. When you are finished, edit the register incrementer so that it again increments by +1.

### 4.3. Reusing a Model with Structural Composition

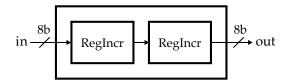

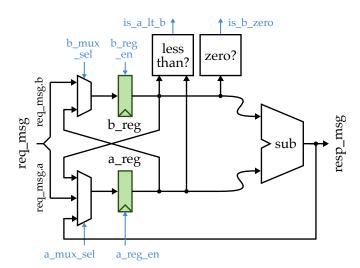

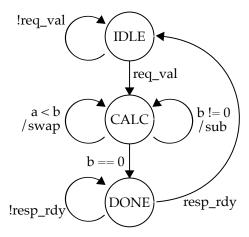

We can use modularity and hierarchy to structurally compose small, simple models into large, complex models. Figure 18 shows a two-stage registered incrementer that uses structural composition to instantiate and connect two instances of a single-stage registered incrementer. Figure 19 shows the corresponding Verilog module. Line 11 uses a 'include to include the child model that we will be

reusing. Notice how we must use the full path (from the root of the project) to the Verilog file we want to include.

Lines 25–31 instantiate the first registered incrementer and lines 35–41 instantiate the second registered incrementer. As mentioned above, we should almost always used named port binding to connect nets to the ports in a module instance. Lines 27–30 illustrate the correct coding convention with one port binding per line and the ports/nets vertically aligned. As shown on lines 26 and 31 the opening and closing parenthesis should be on their own separate lines. We usually declare signals that will be connected to output ports immediately before instantiating the module.

## 4.4. Parameterizing a Model with Static Elaboration

To facilitate model reuse and productive design-space exploration, we often want to implement parameterized models. A common example is to parameterize models by the bitwidth of various input and output ports. The registered incrementer in Figure 16 is designed for only for only eight-bit input values, but we may want to reuse this model in a different context with four-bit input values or 16-bit input values. We can use Verilog *parameters* to parameterize the port bitwidth for the registered incrementer shown in Figure 16; we would replace references to constant 7 with a reference to nbits-1. Now we can specify the port bitwidth for our register incrementer when we construct the model. We have included a library of parameterized Verilog RTL models in the vc subdirectory. Figure 20 shows a combinational incrementer from vc that is parameterized by both the port bitwidth and the incrementer amount. The parameters are specified using the special syntax shown on lines 2–5. By convention, we use a p\_ prefix when naming parameters.

Figure 18: Block Diagram for Two-Stage Registered Incrementer – An eight-bit two-stage registered incrementer that reuses the registered incrementer in Figure 14 through structural composition.

```

// RegIncr2stage

//-----

_{\rm 4} \, // Two-stage registered incrementer that uses structural composition to

5 // instantitate and connect two instances of the single-stage registered

6 // incrementer.

`ifndef TUT4_VERILOG_REGINCR_REG_INCR_2STAGE_V

`define TUT4_VERILOG_REGINCR_REG_INCR_2STAGE_V

10

`include "tut4_verilog/regincr/RegIncr.v"

11

module tut4_verilog_regincr_RegIncr2stage

14

clk,

reset,

input logic

15

16

input logic

input logic [7:0] in,

17

18

output logic [7:0] out

19 );

20

// First stage

22

logic [7:0] reg_incr_0_out;

24

25

tut4_verilog_regincr_RegIncr reg_incr_0

26

.clk (clk),

27

.reset (reset),

28

.in (in),

29

.out (reg_incr_0_out)

);

31

33

// Second stage

tut4_verilog_regincr_RegIncr reg_incr_1

35

36

.clk (clk),

.reset (reset),

.in (reg_incr_0_out),

.out (out)

38

39

40

);

41

42

endmodule

43

44

`endif /* TUT4_VERILOG_REGINCR_REG_INCR_2STAGE_V */

```

**Figure 19: Two-Stage Registered Incrementer** – An eight-bit two-stage registered incrementer corresponding to Figure 18. This model is implemented using structural composition to instantiate and connect two instances of the single-stage register incrementer.

```

module vc_Incrementer

#(

parameter p_nbits = 1,

parameter p_inc_value = 1

| output logic [p_nbits-1:0] in,

| output logic [p_nbits-1:0] out

| output logic [p_

```

Figure 20: Parameterized Incrementer from vc – A combinational incrementer from vc that is parameterized by both the port bitwidth and the incrementer amount.

```

//-----

// RegIncrNstage

//-----

// Registered incrementer that is parameterized by the number of stages.

`ifndef TUT4_VERILOG_REGINCR_REG_INCR_NSTAGE_V

`define TUT4_VERILOG_REGINCR_REG_INCR_NSTAGE_V

include "tut4_verilog/regincr/RegIncr.v"

10

module tut4_verilog_regincr_RegIncrNstage

12 #(

13

parameter p_nstages = 2

14 )(

input logic

input logic

reset,

16

input logic [7:0] in,

17

output logic [7:0] out

18

19 );

// This defines an _array_ of signals. There are p_nstages+1 signals

21

// and each signal is 8 bits wide. We will use this array of signals to

// hold the output of each registered incrementer stage.

23

logic [7:0] reg_incr_out [p_nstages+1];

25

27

// Connect the input port of the module to the first signal in the

// reg_incr_out signal array.

30

assign reg_incr_out[0] = in;

// Instantiate the registered incrementers and make the connections

32

// between them using a generate block.

34

35

genvar i;

generate

for ( i = 0; i < p_nstages; i = i + 1 ) begin: gen</pre>

37

38

tut4_verilog_regincr_RegIncr reg_incr

39

.clk (clk),

41

42

.reset (reset),

.in (reg_incr_out[i]),

43

.out (reg_incr_out[i+1])

44

);

45

46

47

endgenerate

48

50

// Connect the last signal in the reg_incr_out signal array to the

// output port of the module.

52

assign out = reg_incr_out[p_nstages];

55

endmodule

`endif /* TUT4_VERILOG_REGINCR_REG_INCR_NSTAGE_V */

```

**Figure 21:** N-Stage Registered Incrementer – A parameterized registered incrementer where the number of stages is specified using a Verilog parameter.

```

`default_nettype none

`timescale 1ps/1ps

9    include "regincr/RegIncrNstage.v"

include "vc/TestRandDelaySource.v"

include "vc/TestRandDelaySink.v"

12

13 //-----

14 // Testbench defines

15

16

localparam NUM_TESTS = 3;

18 localparam NUM_STAGES = 5;

20 localparam INPUT_TEST_SIZE = 8;

21 localparam OUTPUT_TEST_SIZE = 8;

22

23 //-----

24 // Top-level module

25 //-----

module top( input logic clk, input logic linetrace );

// DUT signals

29

30

logic reset;

31

32

logic

istream_val;

logic [ INPUT_TEST_SIZE-1:0] istream_msg;

33

34

ostream_val;

35

logic [OUTPUT_TEST_SIZE-1:0] ostream_msg;

36

// Source and sink messages

38

logic [ INPUT_TEST_SIZE-1:0 ] src_msgs [ NUM_TESTS-1:0 ];

40

logic [ OUTPUT_TEST_SIZE-1:0 ] snk_msgs [ NUM_TESTS-1:0 ];

41

// Signals to indicate completion

43

logic src_done;

45

logic snk_done;

47

// Module instantiations

49

//-----

50

51

//-----

52

// Test source

54

vc TestSource

56

57

.p_msg_nbits ( INPUT_TEST_SIZE ),

58

.p_num_msgs ( NUM_TESTS )

59

) src (

60

.clk

.clk ( clk), .reset ( reset),

clk),

61

62

63

( istream_val ),

.val

.rdy

.msg

1'b1 ), // Always rdy

65

( 1'b1),

( istream_msg),

66

67

.done

( src_done )

);

69

70

assign src.m = src_msgs;

```

```

72

73

// DUT

74

tut3_verilog_regincr_RegIncrNstage #( NUM_STAGES ) dut

78

79

.clk

clk ),

.reset

reset ),

80

81

( istream_msg ),

82

.in_

83

( ostream_msg )

);

85

86

//-----

87

// Test sink

89

vc_TestSink

91

92

.p_msg_nbits ( OUTPUT_TEST_SIZE ),

.p_num_msgs ( NUM_TESTS ),

94

.p_sim_mode (

1 )

) sink (

96

97

clk ),

.reset (

reset ),

98

99

( ostream_val),

100

/* verilator lint_off PINCONNECTEMPTY */

101

.rdy (

), // Unused

102

/* verilator lint_off PINCONNECTEMPTY */

103