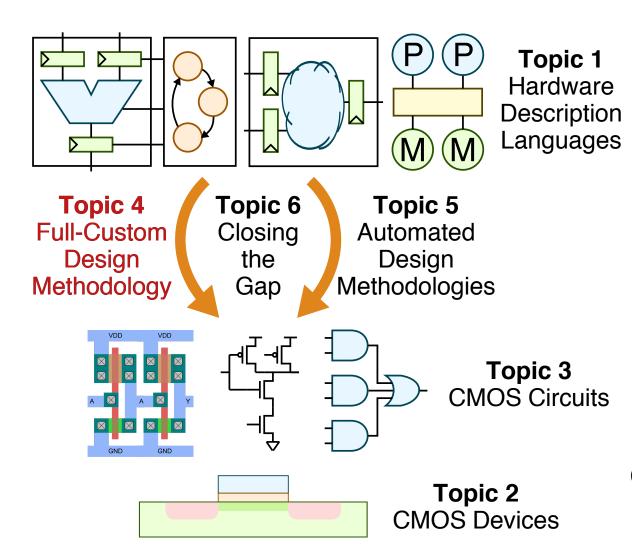

# ECE 5745 Complex Digital ASIC Design Topic 4: Full-Custom Design Methodology

**Christopher Batten**

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece5745

#### Part 1: ASIC Design Overview

**Topic 8**Testing and Verification

Topic 7

Clocking, Power Distribution,

Packaging, and I/O

#### Agenda

#### Design Domains, Abstractions, and Principles

Modularity

Hierarchy

Encapsulation

Regularity

Extensibility

Full-Custom Design

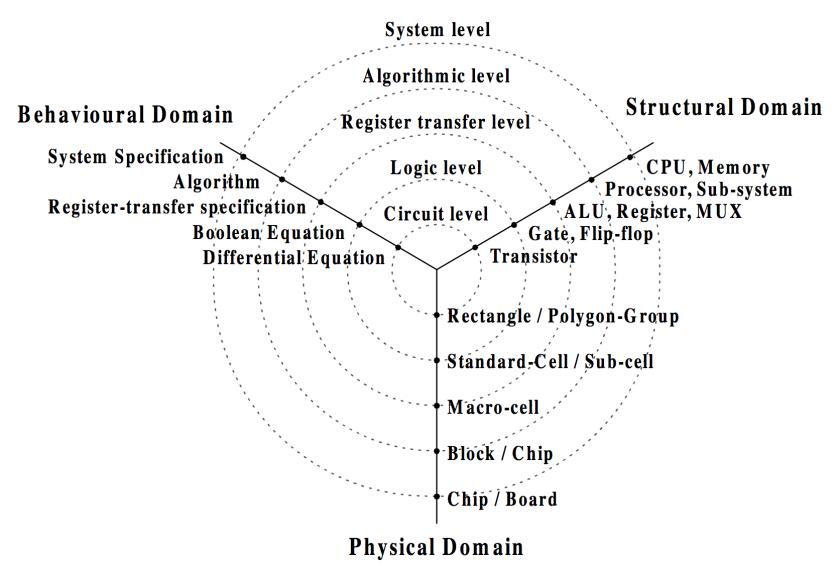

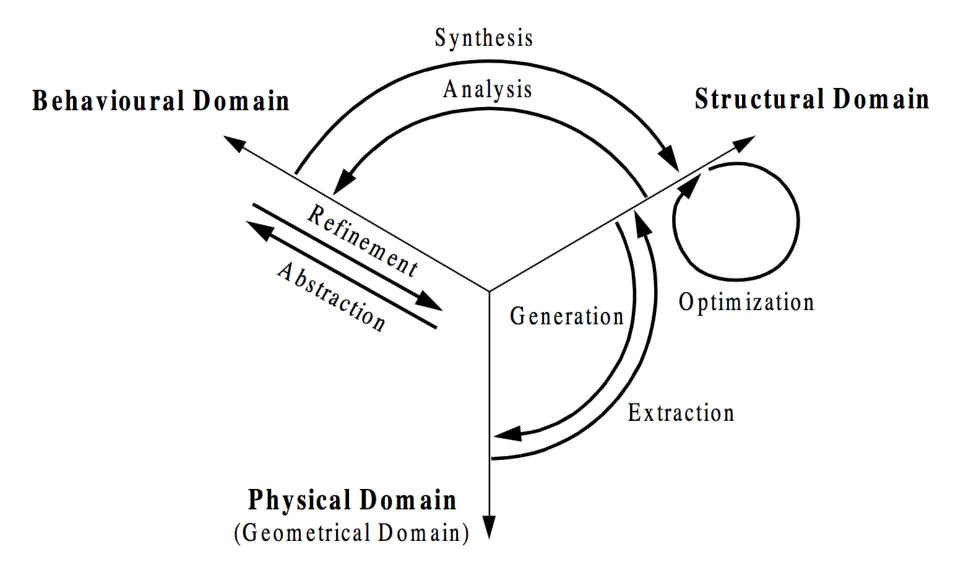

#### Behavioral, Structural, and Physical Abstractions

Adapted from [Ellervee'04]

#### Behavioral, Structural, and Physical Abstractions

Adapted from [Ellervee'04]

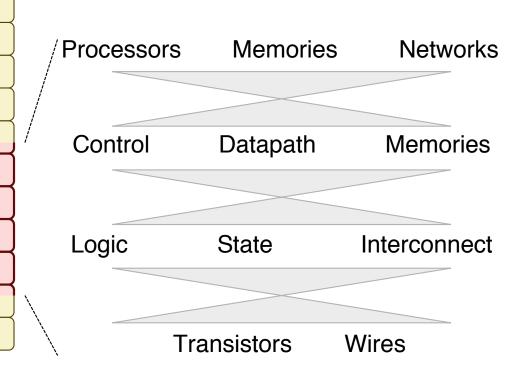

#### **Computer Engineering Stack Abstractions**

**Application**

Algorithm

Programming Language

**Operating System**

Instruction Set Architecture

Microarchitecture

Register-Transfer Level

Gate Level

Circuits

**Devices**

Technology

#### Design Principles in VLSI Design

- Modularity Decompose into components with well-defined interfaces

- Hierarchy Recursively apply modularity principle

- Encapsulation Hide implementation details from interfaces

- Regularity Leverage structure at various levels of abstraction

- Extensibility Include mechanisms/hooks to simplify future changes

#### **Design Principle: Modularity**

- Separate design into components w/ well-defined interfaces

- Reason, design, and test components in isolation

- Interface may or may not encapsulate implementation

#### **Design Principle: Modularity**

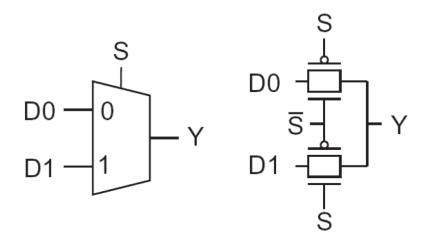

Modularity can also impact electrical and physical characteristics

#### **Electrical Modularity**

What happens if we cascade many of these tranmission gate multiplexers?

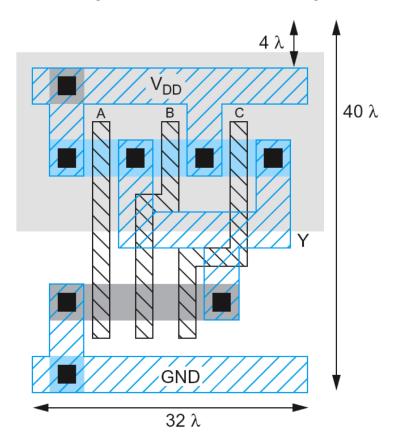

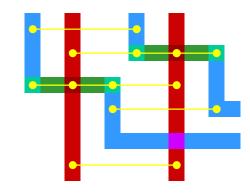

#### **Physical Modularity**

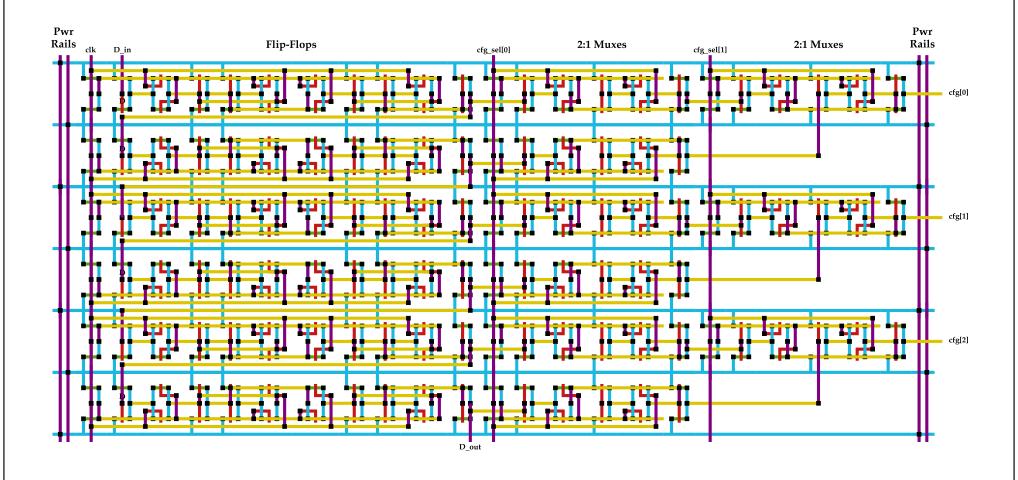

pwr/gnd rails & wells in fixed locations so they connect via abutment Adapted from IV

#### **Design Principle: Hierarchy**

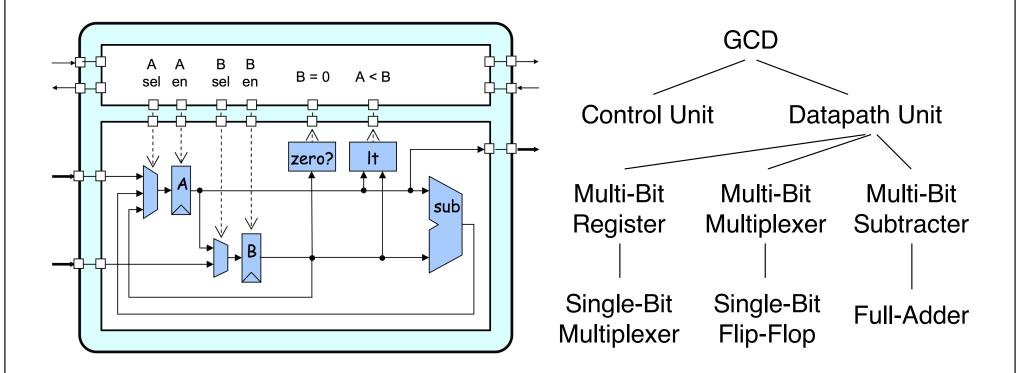

Recursively apply modularity principle until complexity of submodules is manageable

#### **Design Principle: Hierarchy**

#### **Design Principle: Encapsulation**

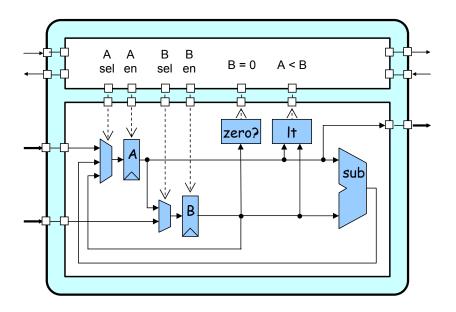

- Modularity requires well-defined interfaces, but these interfaces might still expose significant implementation details (e.g., interface in control/datapath split reveals many details of the implementation)

- Choose interfaces that hide implementation details where possible to enable more robost composition

- Lab 1 multipliers all use a latency-insenstive val/rdy message interface to hide timing details, any one of these can be swaped into a processor and should work without modification

- Fixed-latency iterative multiplier

- Variable-latency iterative multplier

- Pipelined multiplier

#### **Design Principle: Regularity**

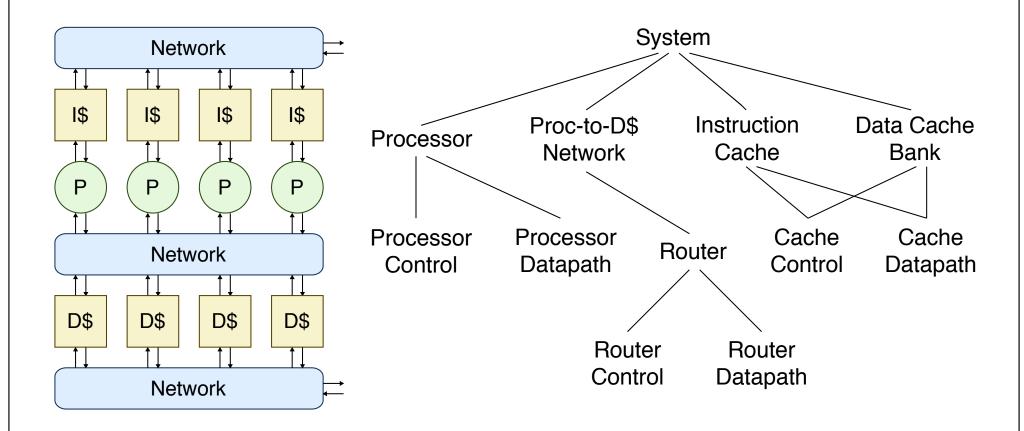

- Modularity, hierarchy, and encapsulation can still lead to many different kinds of modules which can increase design complexity

- Choose a hierarchical decomposition to leverage structure and thus faciliate reuse and reduce complexity

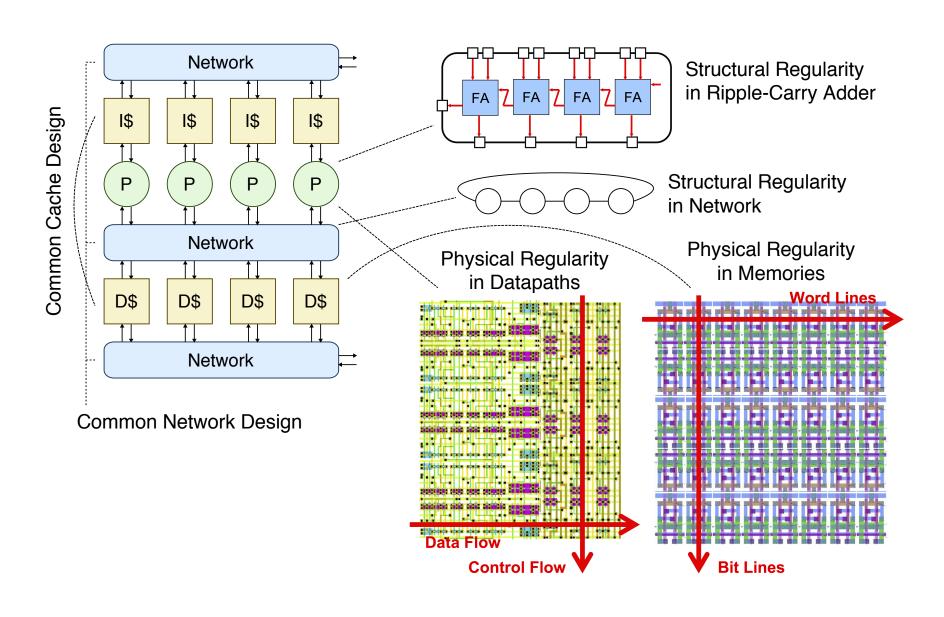

- Both structural and physical regularity can be exploited

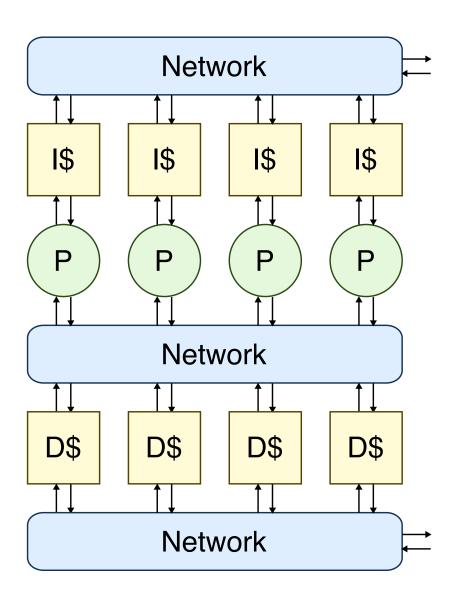

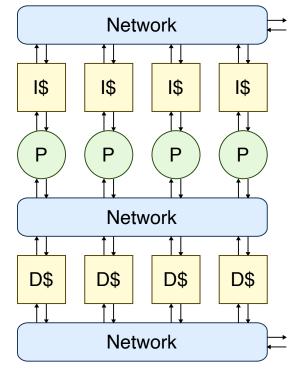

# **Design Principle: Regularity**

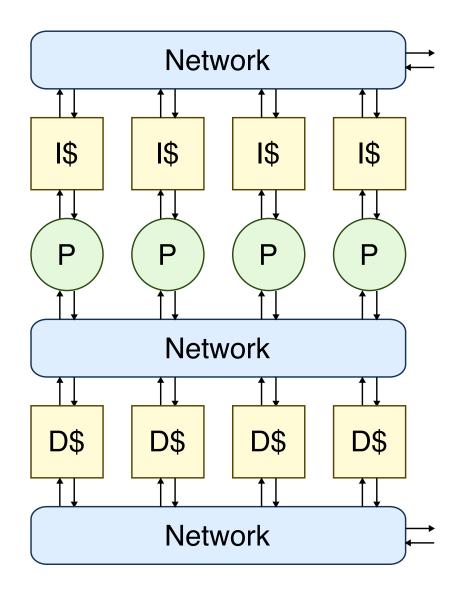

#### **Design Principle: Extensibility**

Simple form of polymorphism enables varying bitwidth of operands

Difficult with full-custom design methodology!

Parameterization of network and caches enables reuse; static elaboration could enable varying the number of cores and the types of components

#### Agenda

Design Domains, Abstractions, and Principles

# Full-Custom Design

Cells

**Datapaths**

**Memories**

Control

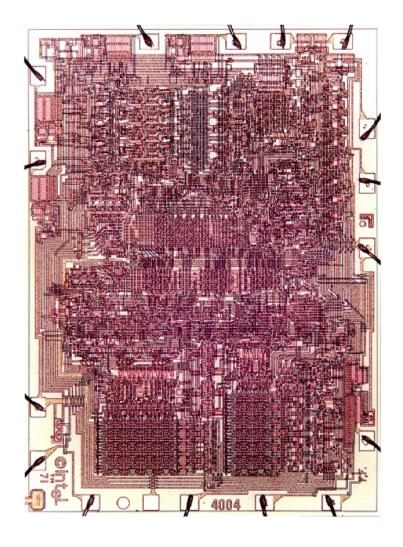

#### **Full Custom Design**

Key is that all circuits and transistors are optimized for specific context

Intel 4004

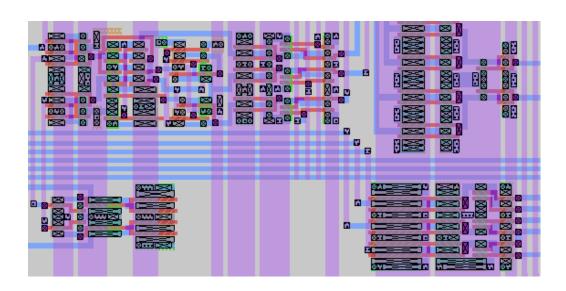

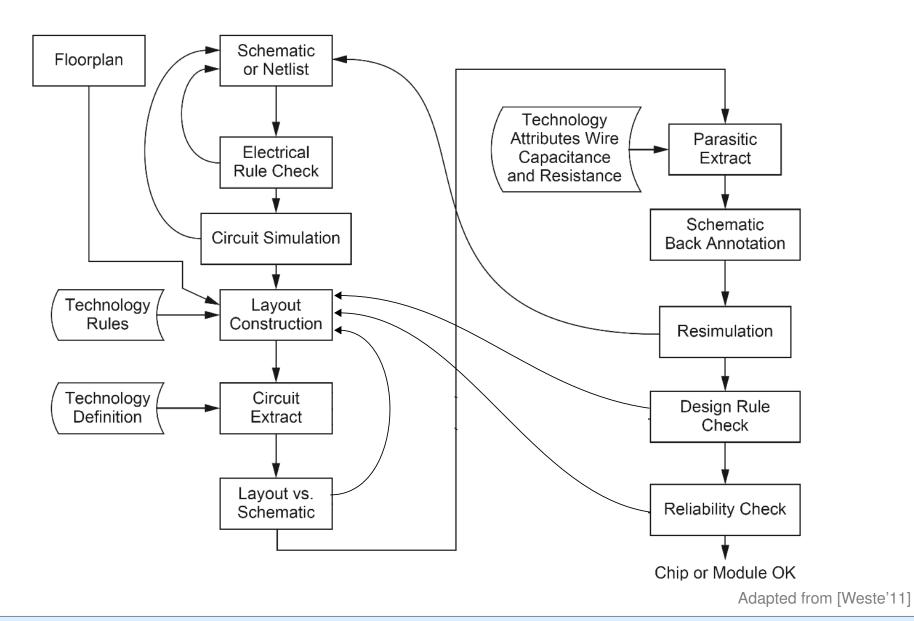

# **Overview of Full Custom Design Methodology**

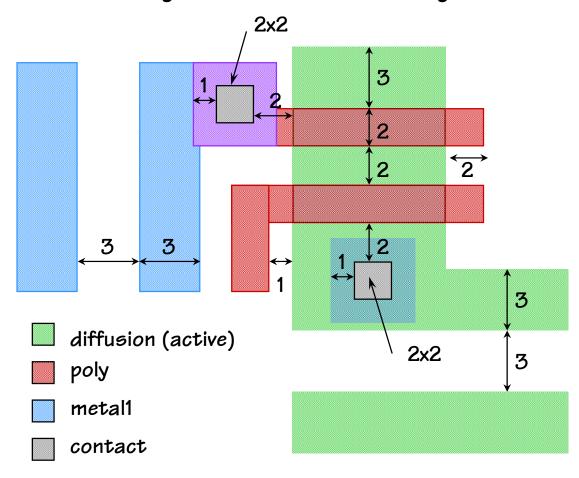

#### **Custom Cells: Lambda-Based Design Rules**

One lambda = one half of the "minimum" mask dimension, typically the length of a transistor channel. Usually all edges must be "on grid", e.g., in the MOSIS scalable rules, all edges must be on a lambda grid.

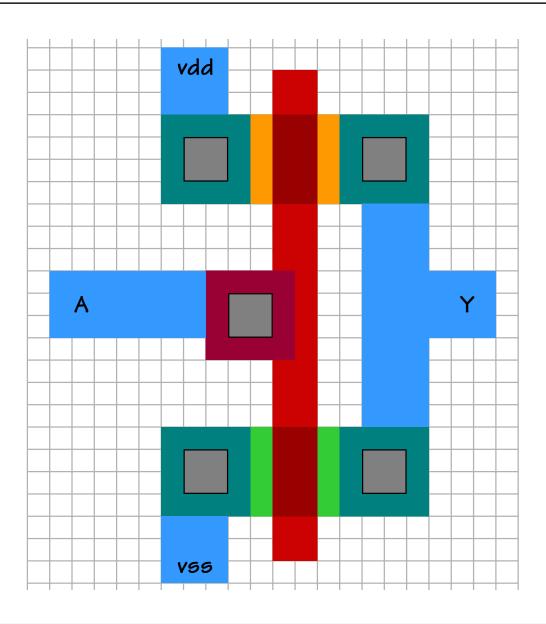

# Custom Cells: Sample "Lambda" Layout

#### Custom Cells: Lambda vs. Micron Rules

Lambda-based design rules are based on the assumption that one can scale a design to the appropriate size before manufacture. The assumuption is that all manufacturing dimensions scale equally, an assumption that "works" only over some modest span of time. For example: if a design is completed with a poly width of  $2\lambda$  and a metal width of  $3\lambda$  then minimum width metal wires will always be 50% wider than minimum width poly wires.

Consider the following data from Weste, Table 3.2:

contacted metal pitch

1/2 \* contact size

contact surround

metal-to-metal spacing

contact surround

1/2 \* contact size

| lambda | lambda | micron             |

|--------|--------|--------------------|

| rule   | = 0.5u | rule               |

| 1λ     | 0.5µ   | 0.375 <sub>µ</sub> |

| 1λ     | 0.5μ   | 0.5μ               |

| 3λ     | 1.5µ   | 1.Ομ               |

| 1λ     | 0.5μ   | 0.5μ               |

| 1λ     | 0.5μ   | $0.375\mu$         |

| 7λ     | 3.5µ   | 2.75 <sub>µ</sub>  |

|        |        | 1                  |

|        |        |                    |

Scaled design is legal but much larger than it needs to be!

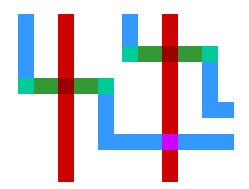

#### **Custom Cells: Sticks and Compaction**

Stick diagram

Horizontal constraints for compaction in X

Compact X then Y

Compact Y then X

Compact X with jog insertion, then Y

# **Custom Cells: Example Stick Diagram**

| inv | v<br>XY  | inv<br>X Y       | tgate<br>enb<br>□ χ<br>□ | Y<br> <br> <br> <br> <br> <br> | inv<br>X Y | inv<br>X Y | tgate<br>enb<br>X   |              | tgate<br>enb<br>□ X        | Y<br>en      | inv<br>XY  | inv<br>X Y | tgate<br>enb<br>□ χ<br>□ | Y<br> <br> <br> <br> <br> <br> | inv<br>X Y<br>Q        | inv<br>X Y<br>Q        | inv<br>XY<br>Q         | tgate<br>enb<br>X        |              | inv<br>X Y<br>Q                            | tgate<br>enb<br>X   | Y<br>-<br>en | inv<br>X Y<br>Q                            | inv<br>X Y<br>Q   | inv<br>X Y<br>Q | tgate<br>enb<br>X | inv<br>X Y<br>Q   | tgate<br>enb<br>□ χ<br>□ | Y in | nv<br>X Y<br>Q |  |

|-----|----------|------------------|--------------------------|--------------------------------|------------|------------|---------------------|--------------|----------------------------|--------------|------------|------------|--------------------------|--------------------------------|------------------------|------------------------|------------------------|--------------------------|--------------|--------------------------------------------|---------------------|--------------|--------------------------------------------|-------------------|-----------------|-------------------|-------------------|--------------------------|------|----------------|--|

|     | XY       | XY               | □ X<br>enb               | en<br>D<br>Y                   | XY         | XY         | _ X<br>enb          | en<br>D<br>Y | □ X<br>enb                 | en<br>D<br>Y | XY         | XY         | □ X<br>enb               | en<br>D<br>Y                   | XY                     | Q<br>D D<br>X Y        | Q<br>Z Y               | _ X<br>enb               | en<br>D<br>Y | Q<br>D D<br>X Y                            | _ X<br>enb          | en<br>D<br>Y | Q<br>D D<br>X Y                            |                   |                 |                   |                   |                          |      |                |  |

| inv | _        | inv<br>inv       | tgate<br>tgate<br>enb    | Y<br>en                        | inv<br>inv | inv<br>inv | tgate tgate enb     |              | tgate<br>tgate<br>enb<br>X |              | -          | inv        | tgate<br>tgate<br>enb    | Y<br>D<br>en                   | inv<br>inv<br>X Y<br>Q | inv<br>inv<br>X Y<br>Q | inv<br>inv<br>X Y<br>Q | tgate<br>tgate<br>enb    |              | inv<br>inv                                 | tgate<br>tgate      |              | inv<br>inv<br>X Y<br>Q                     | inv<br>X Y<br>O Q | inv<br>X Y<br>Q | tgate<br>enb<br>X | inv<br>X Y<br>D Q | tgate<br>enb<br>□ χ<br>□ | Y en | nv<br>XY<br>Q  |  |

| inv | X Y      |                  | □ X<br>enb<br>tgate      | en<br>D<br>Y                   | X Y        | X Y        | □ X<br>enb<br>tgate | en<br>D<br>Y | □ X<br>enb<br>tgate        | en<br>D<br>Y | X Y        | X Y        | □ X<br>enb<br>tgate      | en<br>D<br>Y                   | X Y                    | Q<br>D D<br>X Y        | Q<br>Q<br>X Y          | □ X<br>enb<br>tgate      |              | Q<br>\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | □ X<br>enb<br>tgate | en<br>D<br>Y | Q<br>X Y                                   |                   | ı               |                   |                   |                          |      |                |  |

| inv | v<br>XY  |                  | tgate<br>enb<br>□ χ<br>□ | Y<br>-<br>en                   | inv<br>X Y | inv<br>X Y | tgate<br>enb<br>X   |              | tgate<br>enb<br>□ X<br>□   | Y<br>en      | inv<br>X Y | inv<br>XY  | tgate<br>enb<br>X        | Y<br>                          | inv<br>X Y<br>Q        | inv<br>X Y<br>Q        | inv<br>X Y<br>Q        | tgate<br>enb<br>□ X<br>□ | Y<br>en      | inv<br>X Y<br>Q                            | tgate<br>enb<br>X   | Y<br>        | inv<br>X Y<br>Q                            | inv<br>X Y<br>Q   | inv<br>X Y<br>Q | tgate<br>enb<br>X | inv<br>X Y<br>Q   | tgate<br>enb<br>□ X<br>□ | Y en | X Y<br>Q<br>Q  |  |

| inv | X Y<br>v | □□<br>X Y<br>inv | □ X<br>enb<br>tgate      | en<br>D<br>Y                   | X Y        | X Y        | □ X<br>enb<br>tgate | en<br>       | □ X<br>enb<br>tgate        | en<br>D<br>Y | X Y        | X Y        | □ X<br>enb<br>tgate      | en<br>D<br>Y                   | X Y                    | Q<br>N Y<br>inv        | Q                      | □ X<br>enb<br>tgate      | en<br>D<br>Y | Q<br>D D<br>X Y<br>inv                     | □ X<br>enb<br>tgate | en<br>□<br>Y | Q<br>\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ inv |                   |                 |                   |                   |                          |      |                |  |

#### **Custom Cells: Example Stick Diagram**

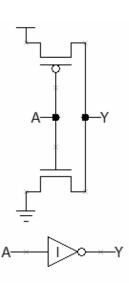

#### Custom Cells: Cell "Styles"

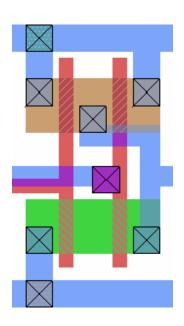

#### **Vertical Gates**

Good for circuits where fets sizes are similar and each gate has limited fanout. Best choice for multiple input static gates and for datapaths.

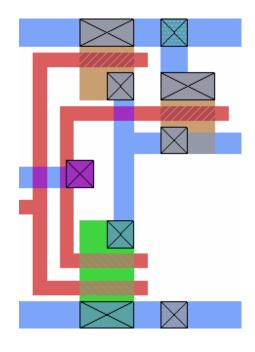

#### Horizontal Gates

Good for circuits where long and short fets are needed or where nodes must control many fets. Often used in multiple-output complex gates (e.g, sum/carry circuits).

What about routing signals between gates? Note that both layouts block metal/poly routing inside the cell. Choices: metal2 routing over the cell or routing above/below the cell.

- avoid long (> 50 squares) poly runs

- don't "capture" white space in a cell

- don't obsess over the layout, instead make a second pass, optimizing where it counts

#### **Custom Cells: Optimizing Connections**

Which does this gate do? Which is better considering node capacitances?

#### **Custom Cells: Optimizing Large Transistors**

Which is better considering wire resistances? Which is better considering node capacitances?

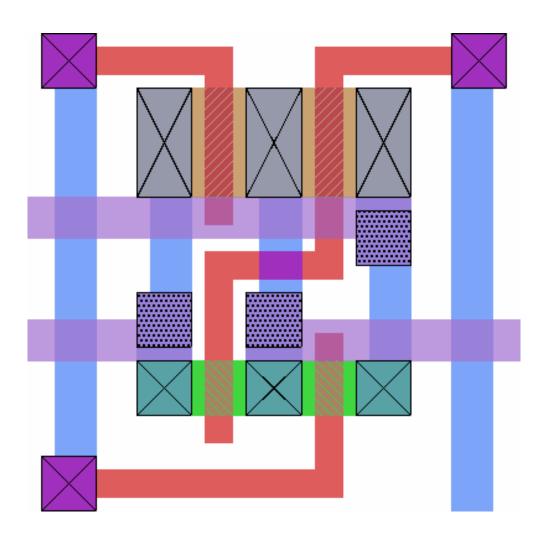

### **Custom Cells: Optimizing Diffusion Sharing**

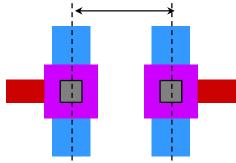

#### **Custom Cells: Optimizing Across Cells**

What does this cell do?

What if we want to replicate this cell vertically to process many bits in parallel?

#### **Custom Cells: Optimizing Across Cells**

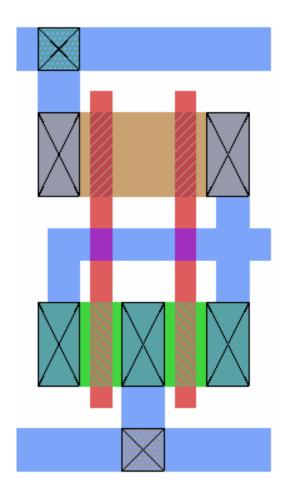

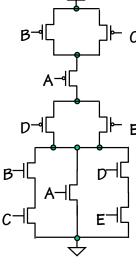

#### **Custom Cells: Merging Simple Cells**

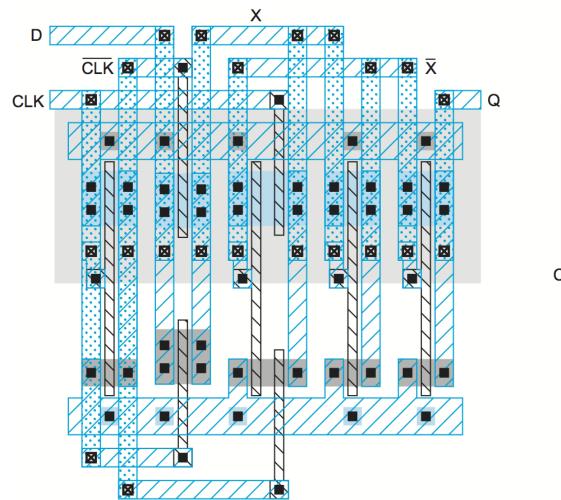

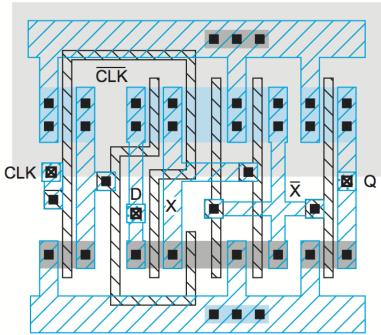

Two latch implementations: Left implementation composes primitive gates, while right implementation uses single tightly integrated gate

Adapted from [Weste'11]

### **Custom Datapaths, Memories, Control**

#### **Custom Datapaths, Memories, Control**

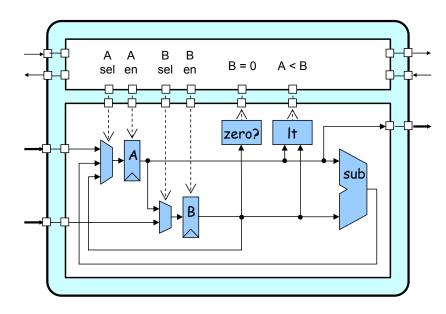

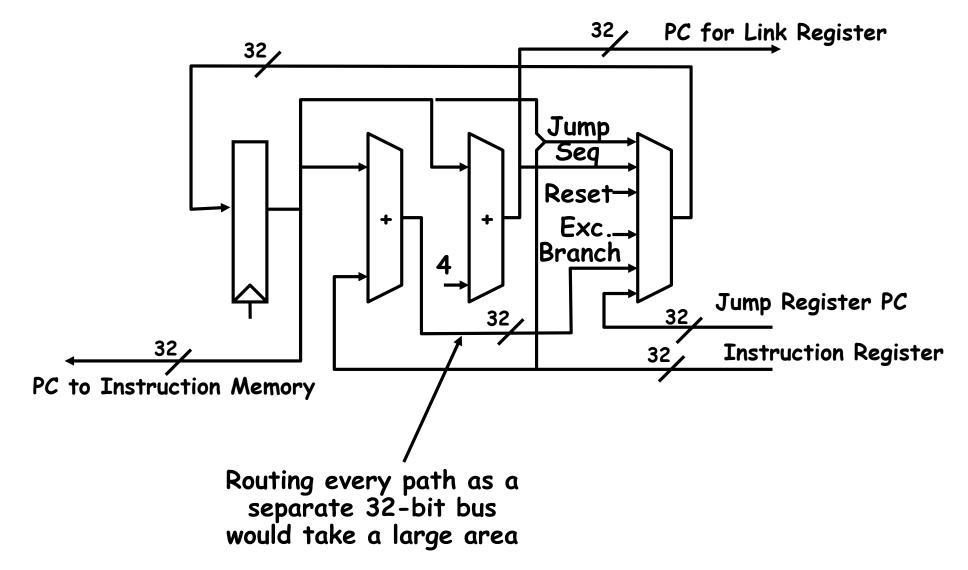

#### **Custom Datapaths: PC Generation Unit**

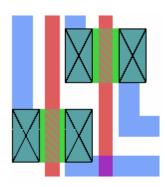

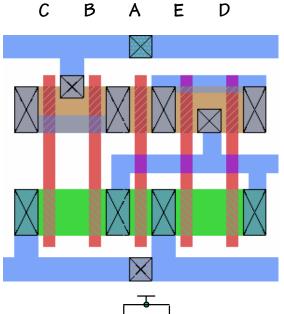

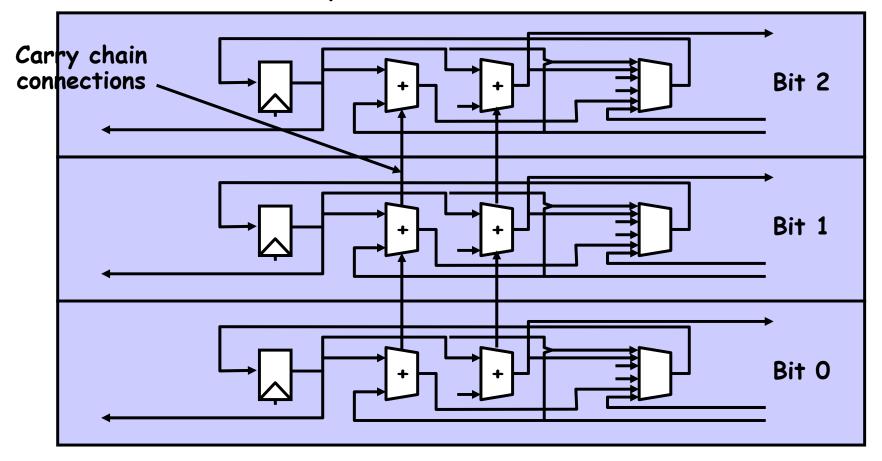

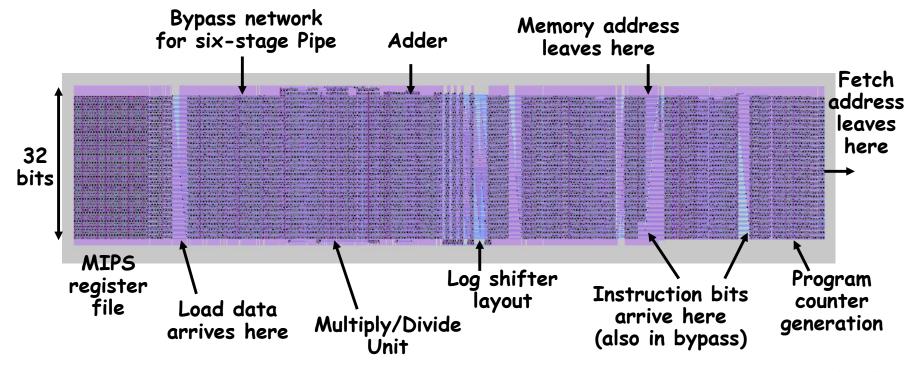

#### **Custom Datapaths: Bitslices**

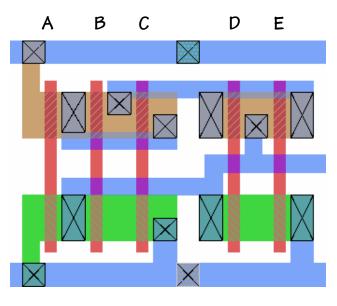

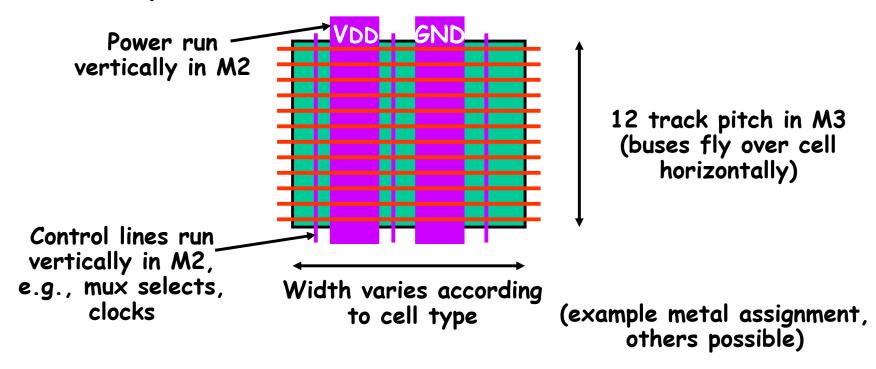

- Implement datapath as single bit slices, contain one bit from each functional unit

- Route each bus bit position within bitslice

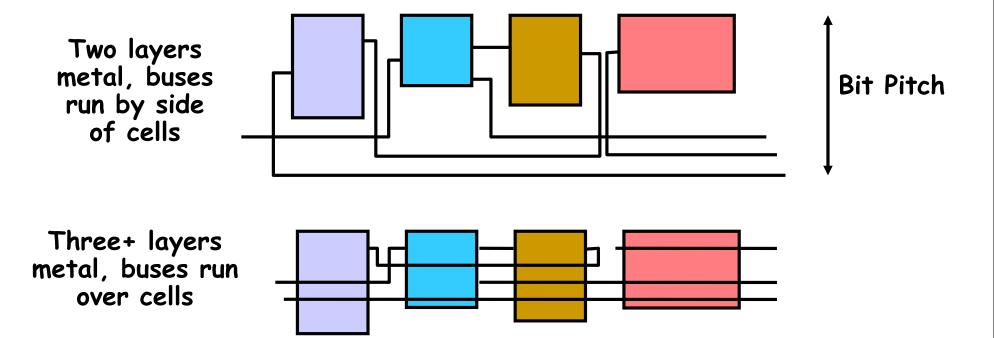

#### **Custom Datapaths: Bit Pitch**

- Height of each bit slice depends on:

- height of tallest cell in entire bitslice

- maximum number of buses running through any cell in bitslice

### **Custom Datapaths: PC Gen Example**

Bus rip out at right angles

Buses' routed by side of cells

In 1.0 µm, 2-metal CMOS process

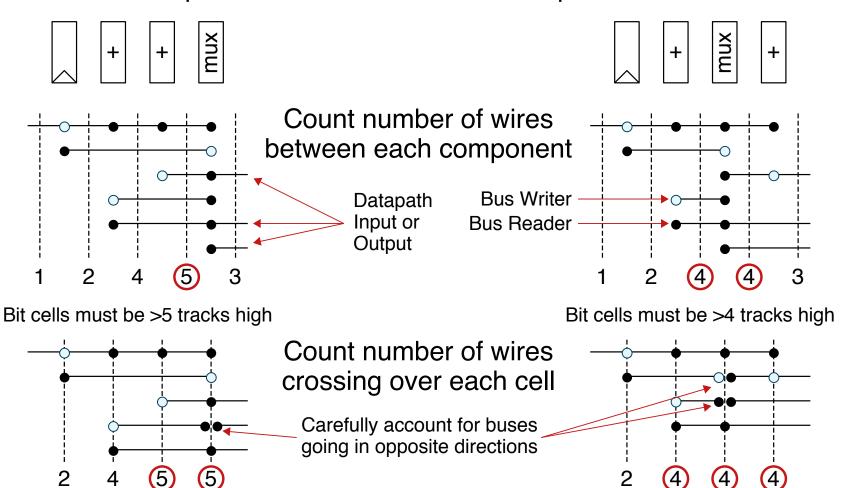

## **Custom Datapaths: Datapath Library Cells**

- Have to choose maximum datapath cell height

- Too high, wastes area in simple cells

- Too small, squeezes complex cells. Grow superlinearly in length dimension, so also wastes area.

- Compromise, around 8-12 metal tracks works OK

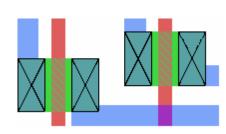

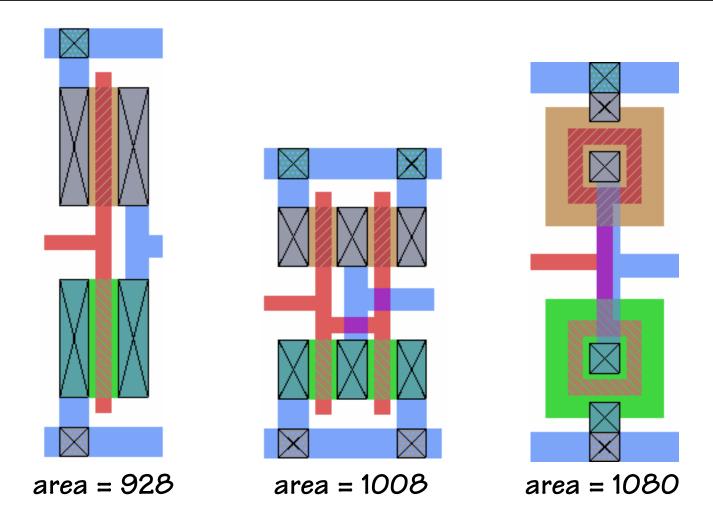

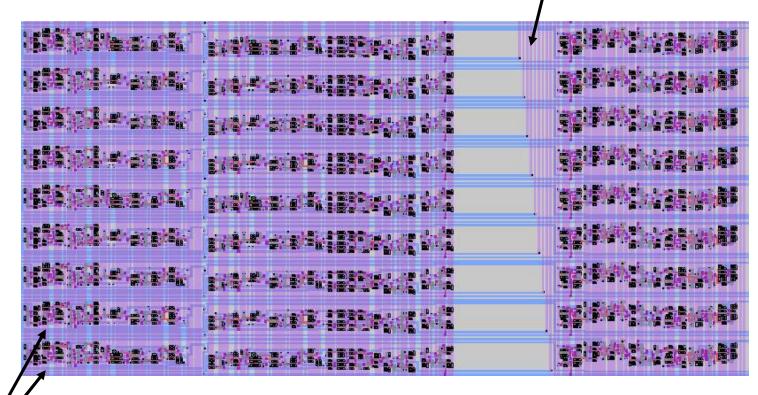

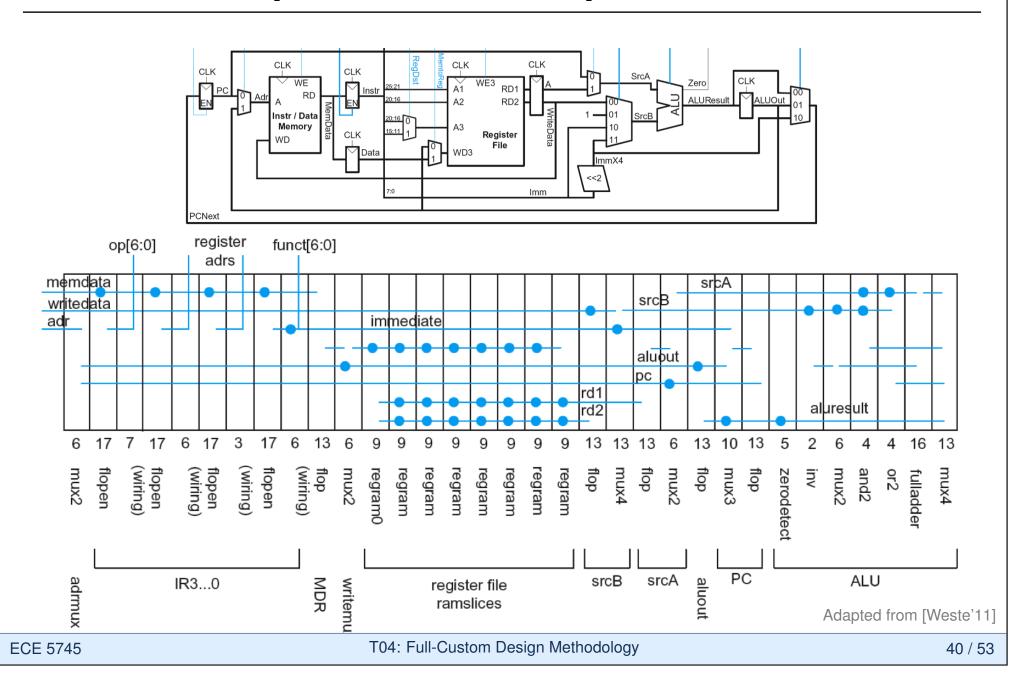

# **Custom Datapaths: Optimizing Datapath Layout**

Reduce congestion by rearranging datapath components to minimize required number of vertical tracks per bitslice

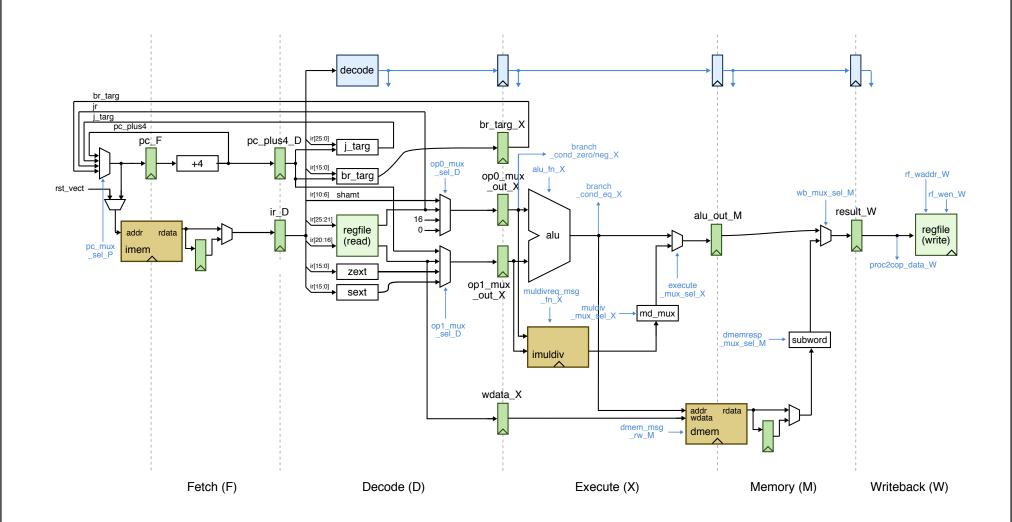

### **Custom Datapaths: MIPS Datapath Track Allocation**

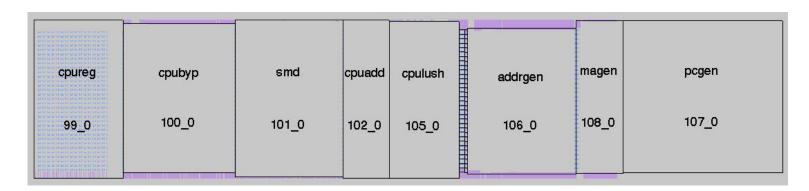

# **Custom Datapaths: MIPS Datapath Example (1)**

# **Custom Datapaths: MIPS Datapath Example (2)**

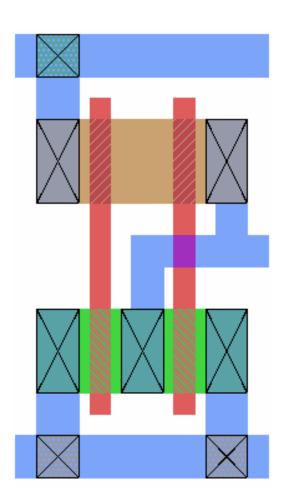

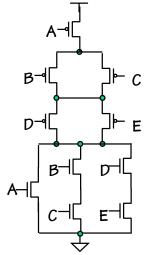

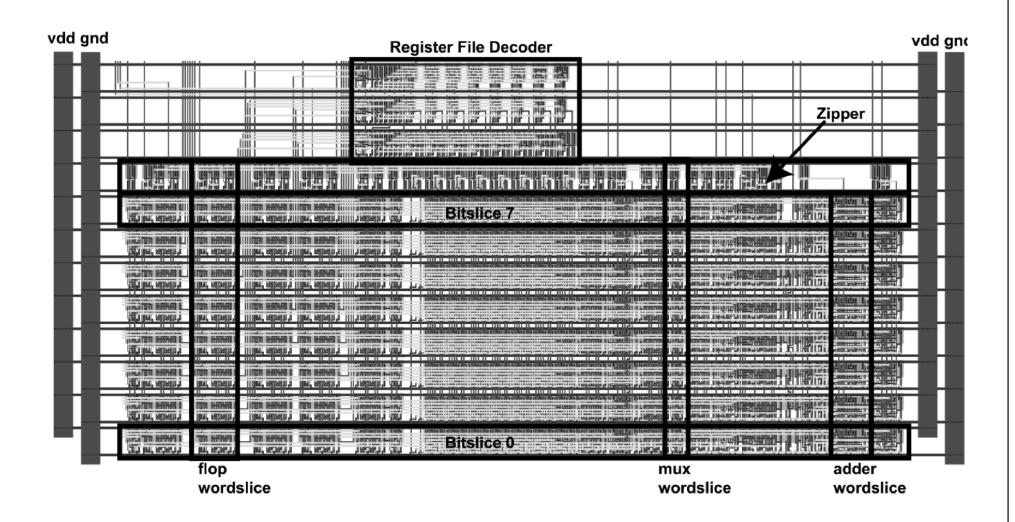

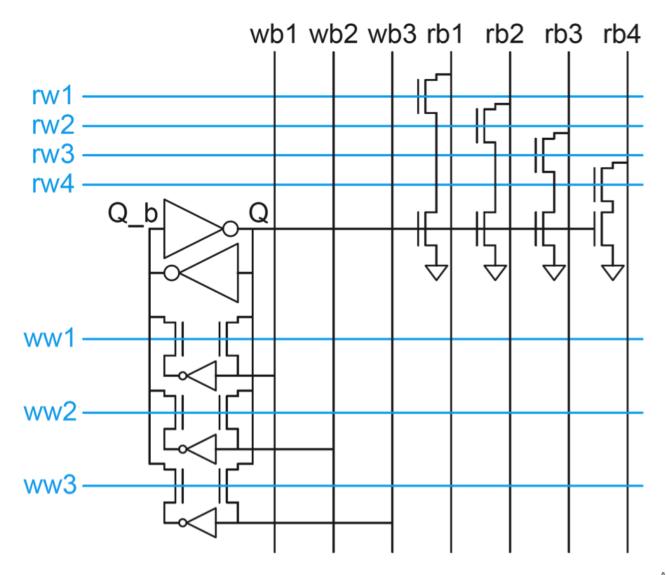

# **Custom Memories: Register File Circuits**

## **Custom Memories: Register File Circuits**

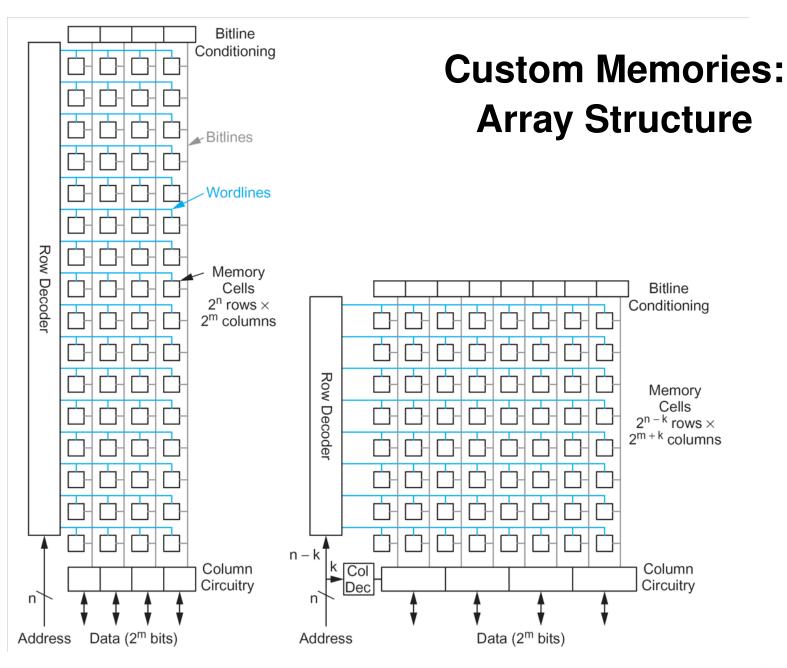

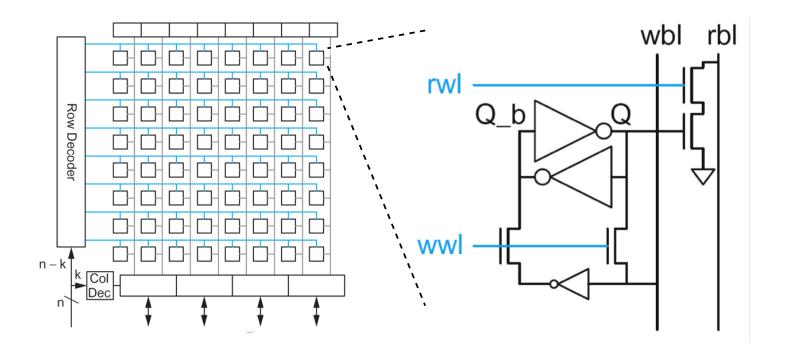

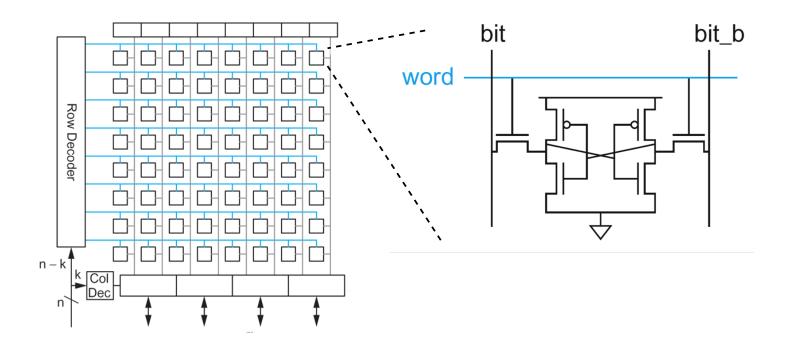

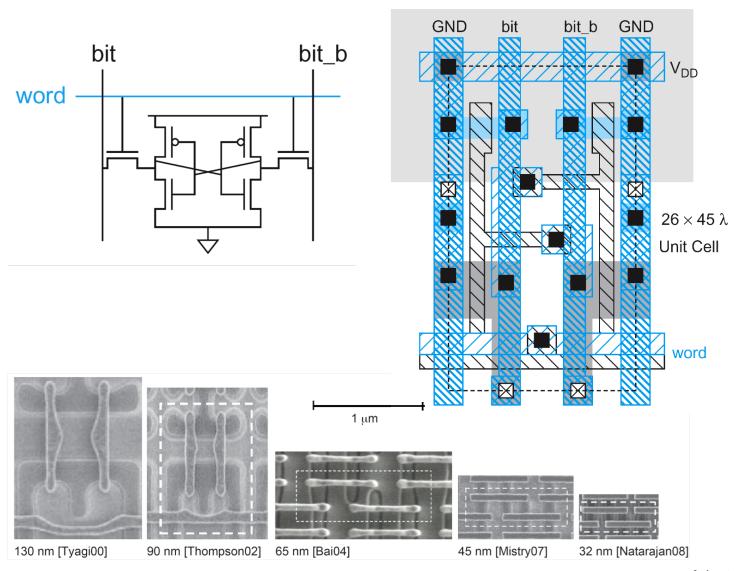

### **Custom Memories: SRAM Circuits**

## **Custom Memories: SRAM Layut**

Adapted from [Weste'11]

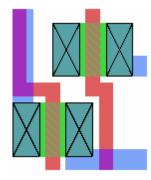

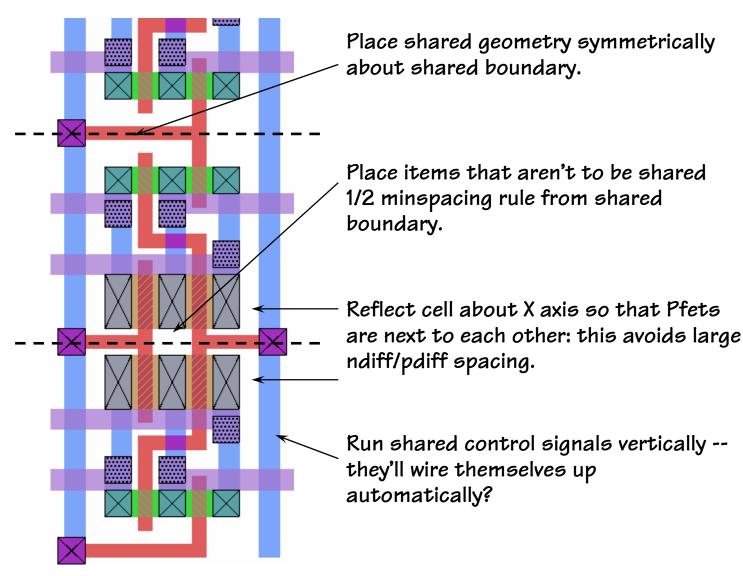

#### **Custom Memories: SRAM**

- Regular arrays built with cells that abut in two dimensions

- Have to pitch match in both dimensions

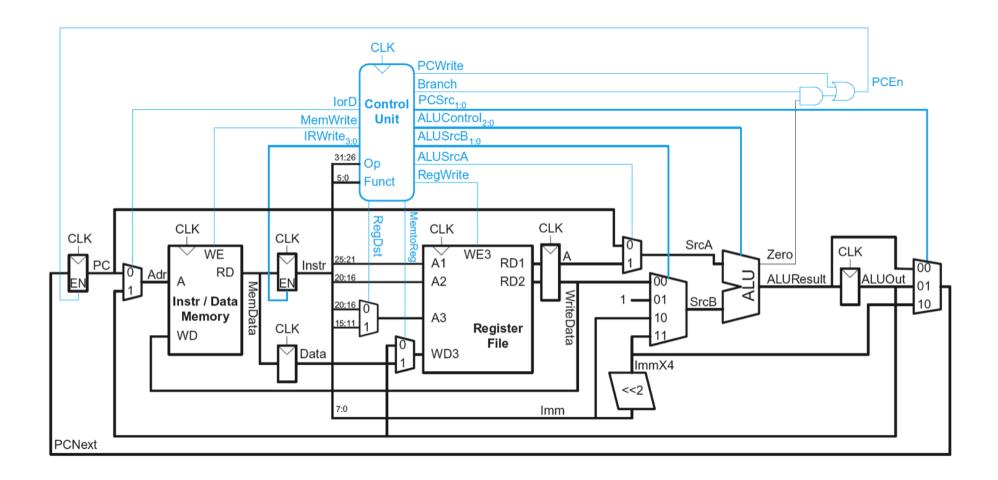

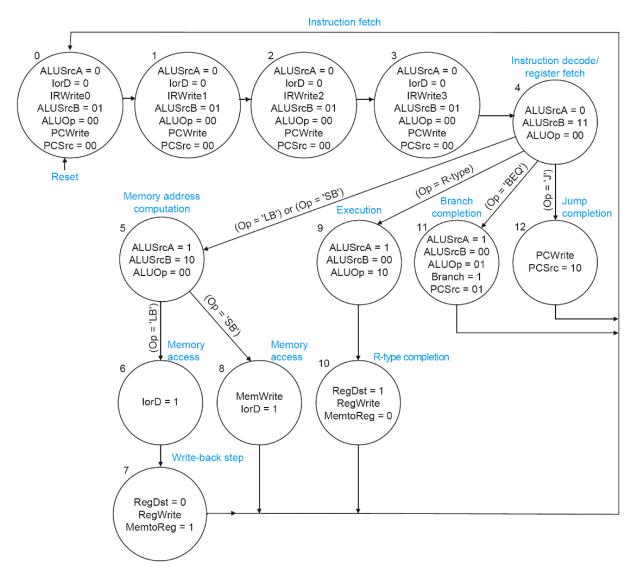

#### Finite-State-Machine Control Unit

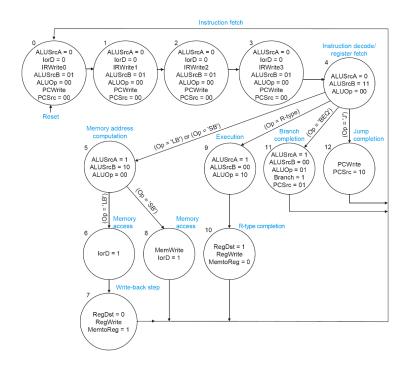

### **Full Custom Control Logic with PLA**

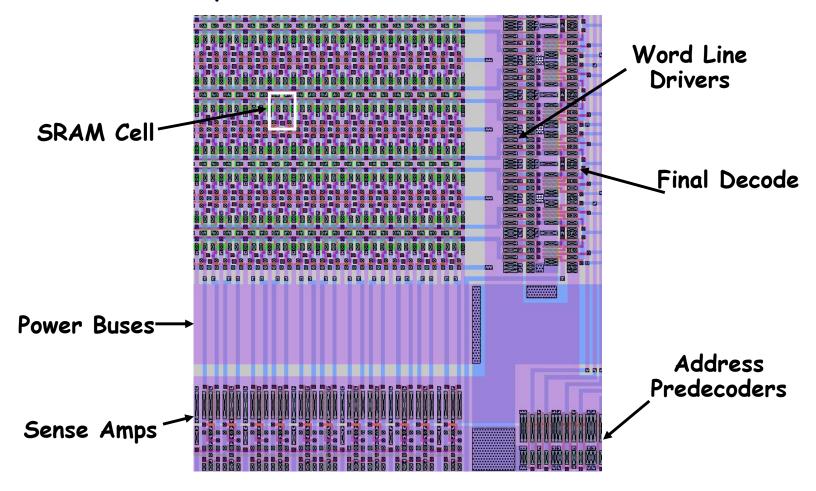

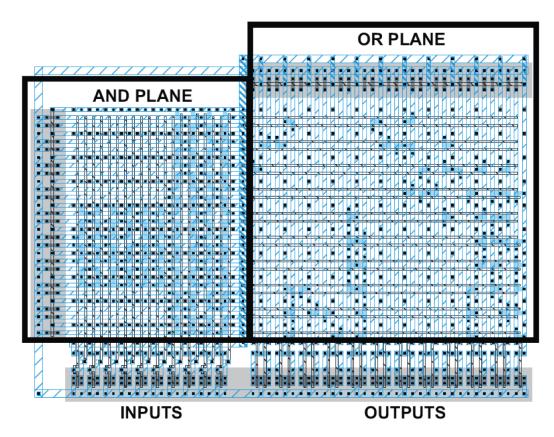

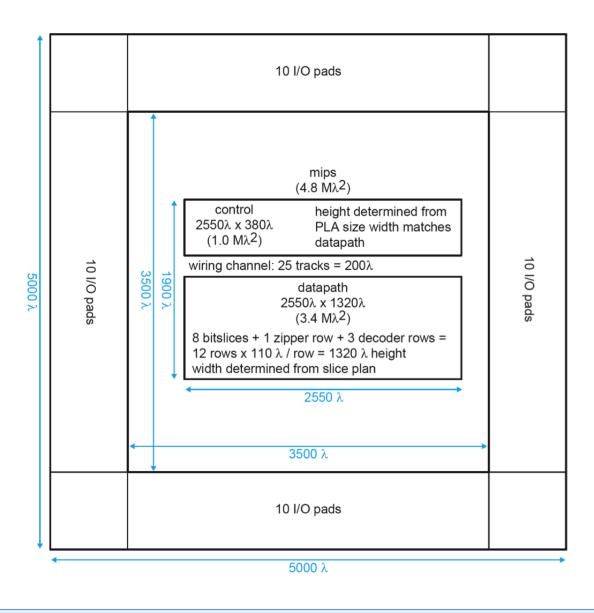

## **Top-Level Chip Floorplan**

Adapted from [Weste'11]

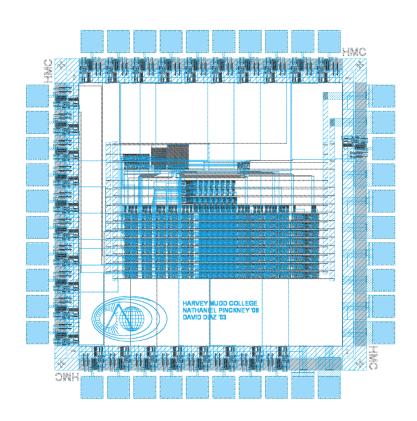

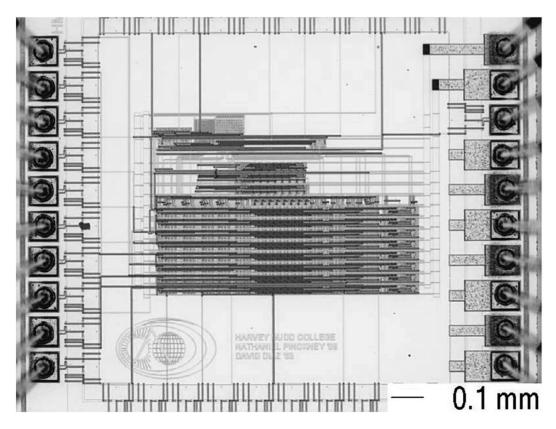

### **Final Full-Custom MIPS Processor**

### **Acknowledgments**

- [Weste'11] N. Weste and D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective," 4th ed, Addison Wesley, 2011.

- [Terman'02] C. Terman and K. Asanović, MIT 6.371 Introduction to VLSI Systems, Lecture Slides, 2002.

- ► [Ellervee'04] P. Ellervee, IAY3714 VLSI Synthesis and HDLs, Lecture Slides, 2004.