# ECE 5745

109 CMOS CONBINATIONAL LOGIC

- LOGICAL EFFORT

ENERGY AREA

Access Ac

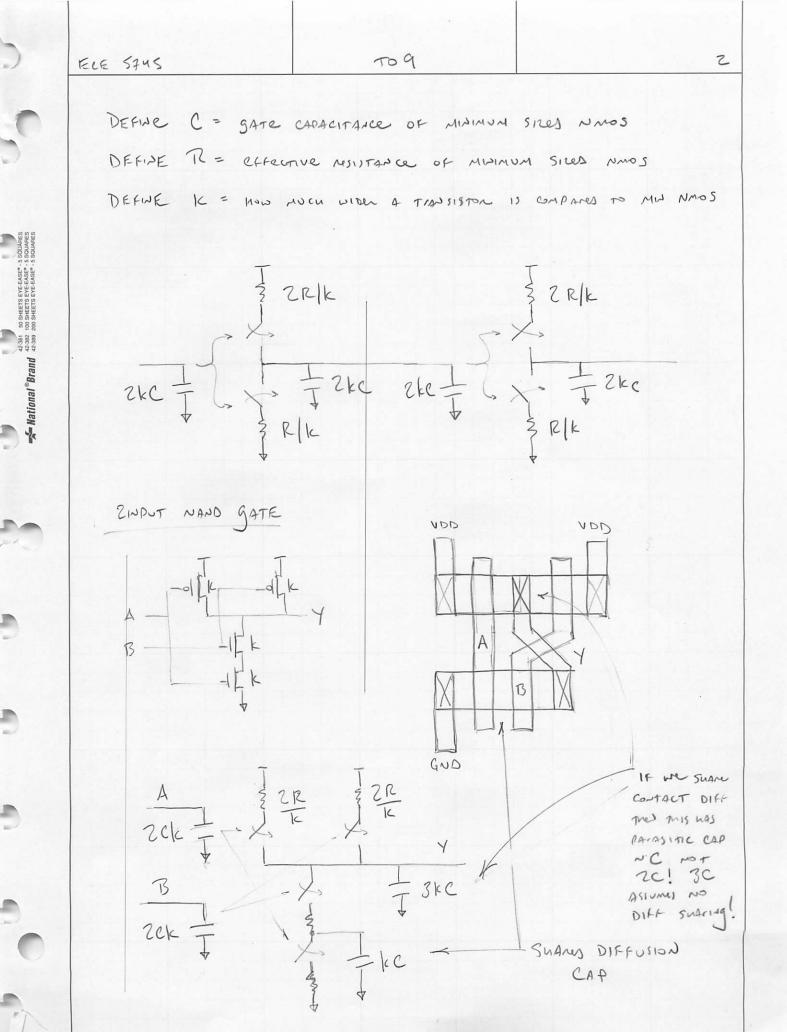

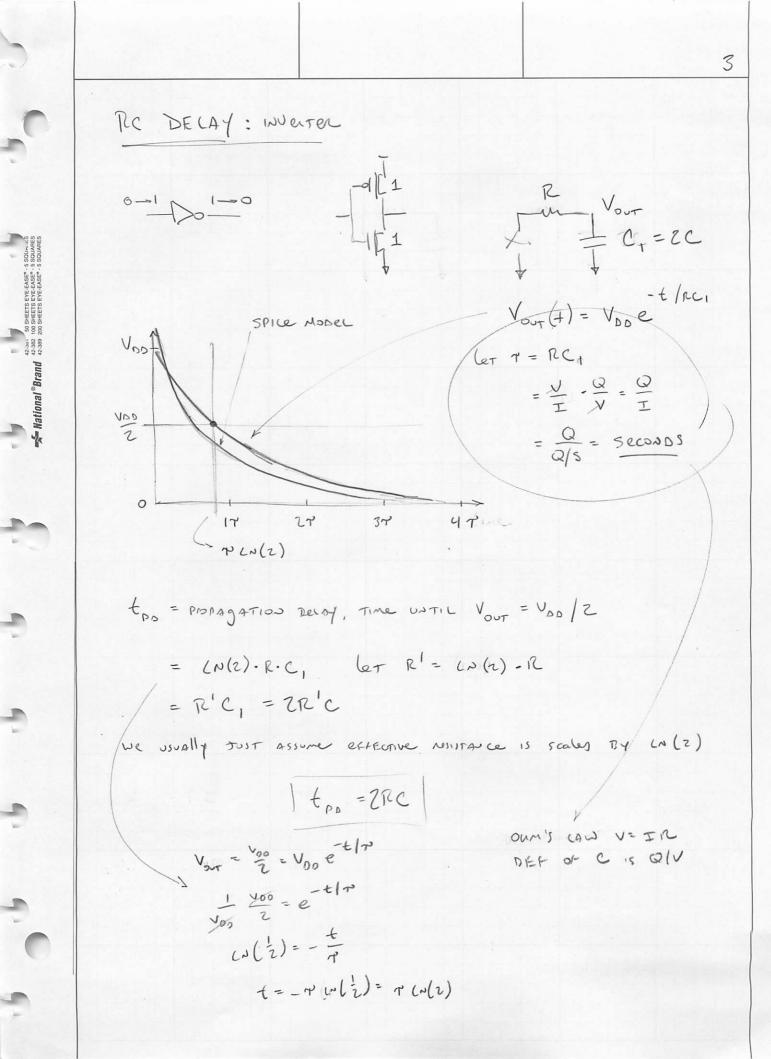

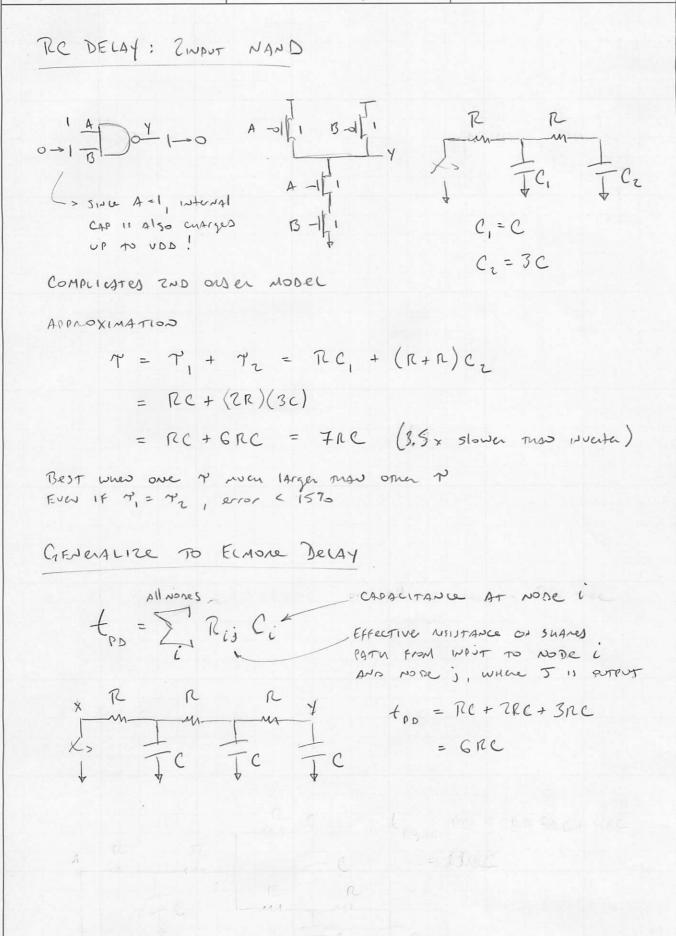

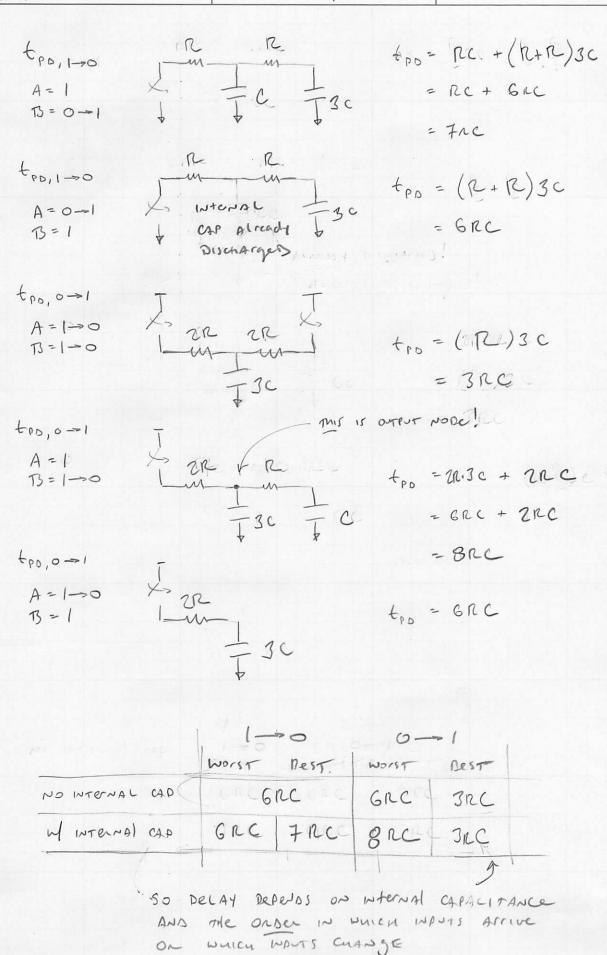

RC MODELS

DELAY - RC Models - RC DELAY

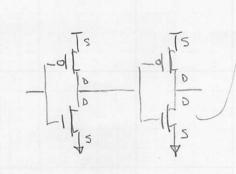

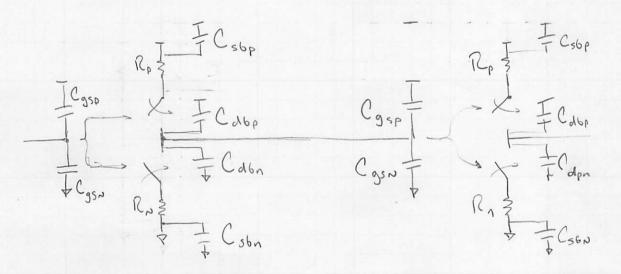

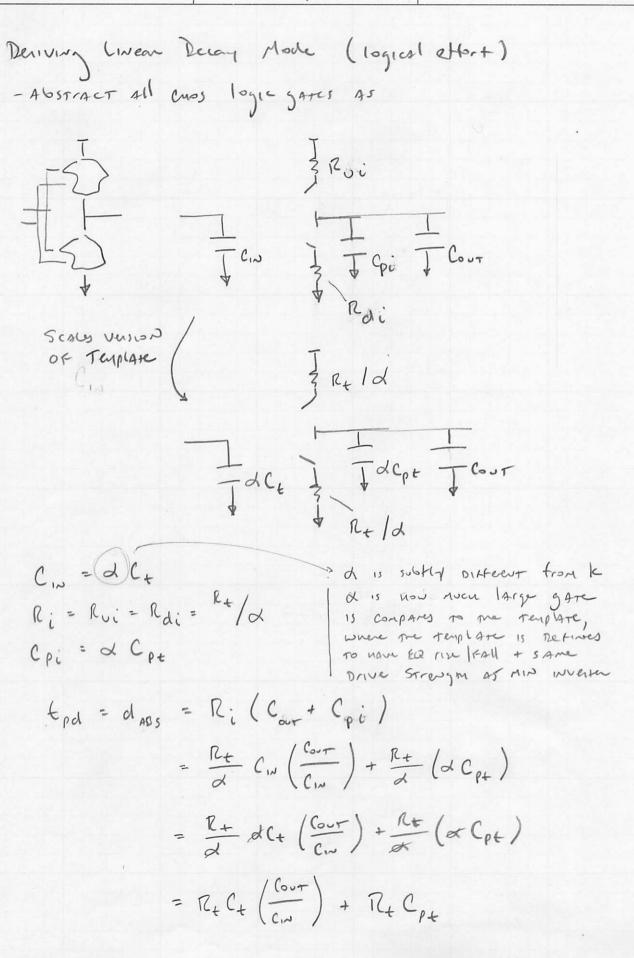

- CS6 CAPACITONS DO NOT ACMAILY SWITCH, SO IGNORE - LUMP COBP + COBN SIJCE BOTH TIES TO CONSTANT NODES - LUMP Casp + Caso Since nom men to GNIFAIT NOMS - A Ssume pros MOBILITY 2x Work MAN NMOS Mobility

ELE STUS

A National Brand 4200 to SHEETS EVE EASE\* 6 SOUNDS

109

EEE 5745

5 3

A - 1 00 SHEETS FREEKER' - 5 Se. VIS 42.802 100 SHEETS FREEKER' - 5 SOUNES 42.802 200 SHEETS FREEKER' - 5 SOUNES 42.803 200 SHEETS FREEKER' - 5 SOUNES

-

## ECE STUS

-

TOG

6

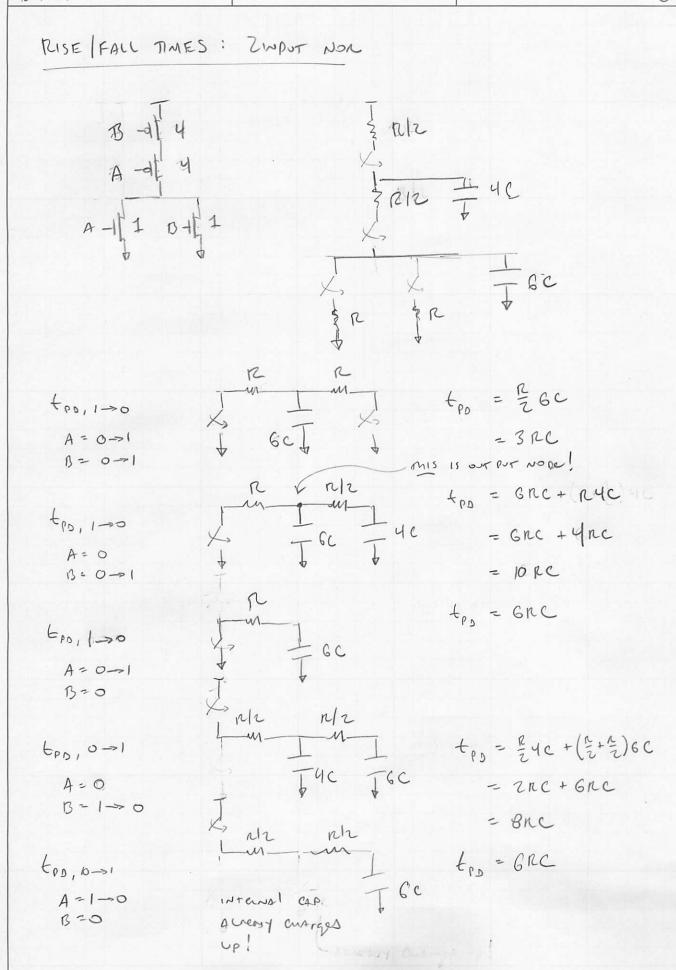

RISE FAIL TIMES : INVENTO Front EARLIER tpo, 1-0 = 2AC unequal JZR ZZR Rise FAIL TIMES Epo,0=1 = 4RC 7 20 FOR EQUAL RISE FAIL TIMES, THE EFFECTIVE rolt 2 RESULTANCE OF PULLUP MUT EQUAL REFECTIVE RISUTANCE OF PULL DOWN W- FOUT 1-15 1 IF we assume PMOS MOBILITY 2x wonce man NMOS, THE PMOS MUST BE 2x SIZE OF (= tpo, 1->= 3RC NMOS IN AN INVERTER FOR EQUAL RISE/FAIL Epp, 0->1 = 3RC RISE FAIL TIMES : ZINDUT NAND SIZY TRANSISTONS 50 WORST CALL EFFERTIVE RESISTANCE EQUAL IN BOM PULL UP AND PULL DOWN NERWORKS A-of I Bal I WORST STR STR care EFFERTIVE NEUISTANCE NESIS TONCE A-111 0-111 =2R RR T3C WOIST CASE XS TCC FRECTUR - Assumes worst case NSITANLE where only A single =2R PMOS is pulling up OUTPUT NORE J

ECE STUS

0

Annual Brand Actions

5

-

#### 009

## ECESTUS

####

ELES745

SOUARES SOUARES SOUARES

> EYE-EASE<sup>®</sup> -EYE-EASE<sup>®</sup> -EYE-EASE<sup>®</sup> -

C

1

|         | 1               | tpo, 1-00<br>worst neit | Woist Best |

|---------|-----------------|-------------------------|------------|

| rventer |                 | 3.RC                    | 3.KC       |

| NAND    | NO INTERNAL CAD | Gric                    | GRC 3rc    |

|         | NO INTERNAL CAD | 7RC/ GRC                | BAC 3AC    |

| Non     | No interal cap  | GRC 3RC GRC)            |            |

|         | wo interal cap  | IORC BAC                | BRC GRC    |

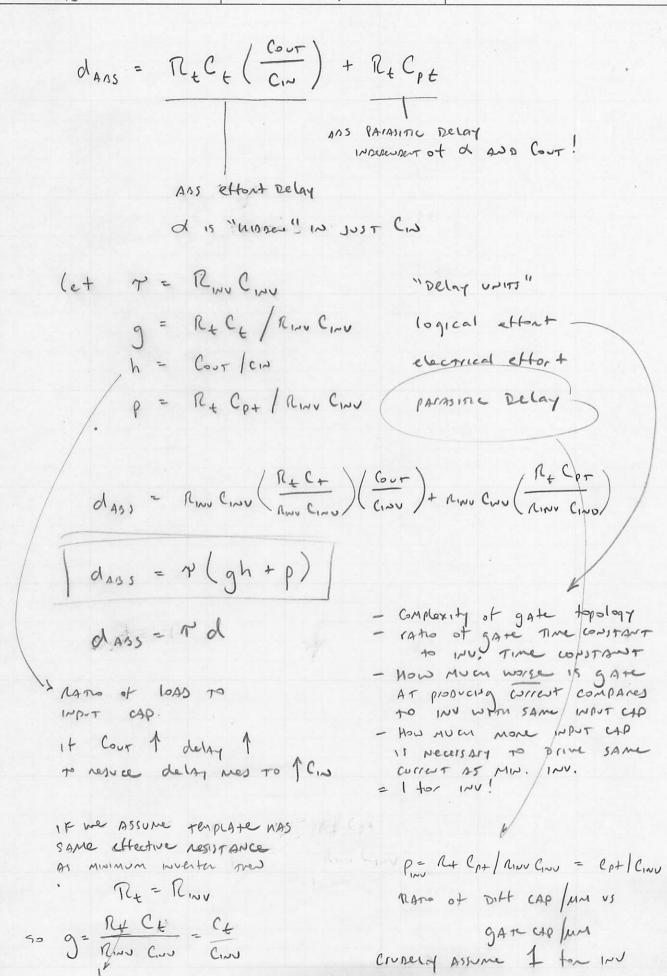

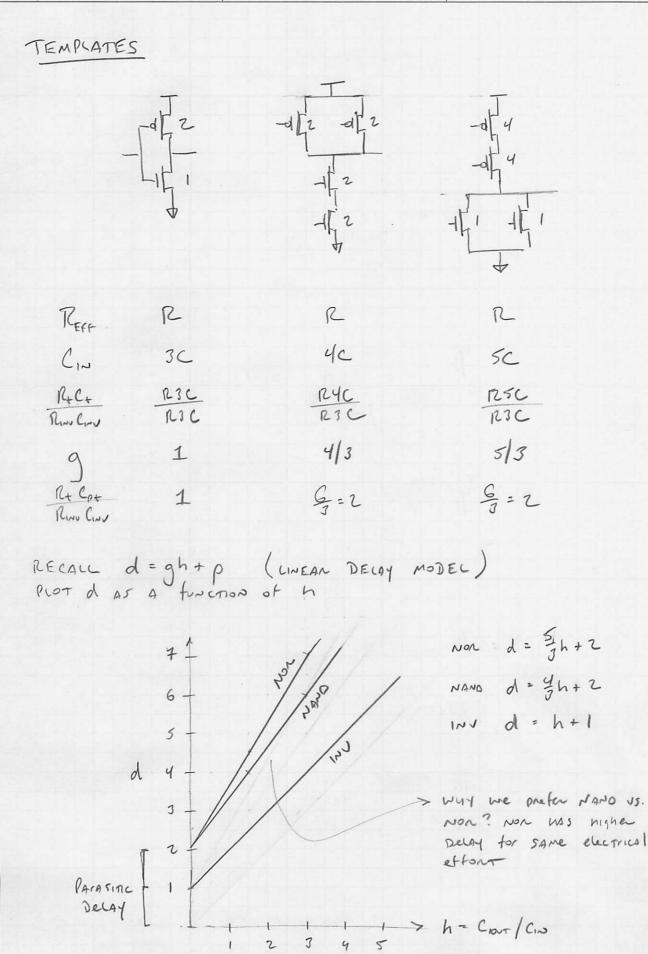

IS THIS A FAIR COMPARISON? NO, WE ARE NOT NORMALIZING ANY THING A CROSS THELE GATES. NEED TO EITHER NORMALIZE

1) INPUT GATE CAP (IR. LOAD ON PREVIOUS GATE)

2) Drive strength (1e. effective resistance)

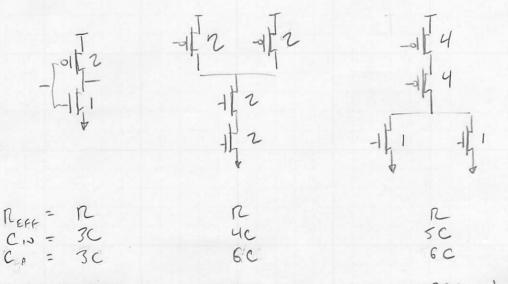

EFFECTIVE MESSIFANCE OF All 3 GATES

NAVO RE SOMALE THE DRIVE AUSISTATCE

Here Are All three GATES SIZED to have EQUAL rise AND FAIL TIMES AND THE SAME Drive Strangth

Epp, 150 - 3.RC GRC GRC ) Ignone int cap top, 0-51 - 3.RC GRC GRC Worst case

ECE STUS

#### 109

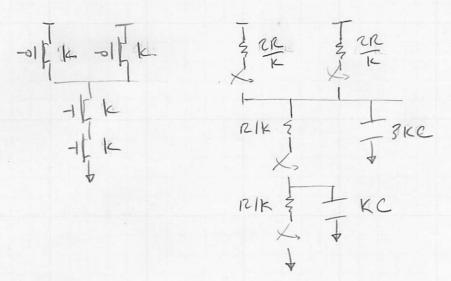

LARGER GATES

Worst Case

A National®Brand 42-882 100 51

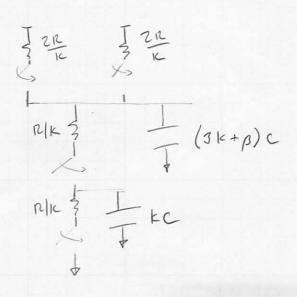

+PO,1->0 = RKC + (R+R)3.KC = FRC SAME As Refore. tro, 0-1 = ZR . 3.KC + (2R ) KC = 9RC /

This is the PARASITIC DELAY, IT IS INDEPENDENT OF SIZE

LARGER LOADS

ECESTUS

tpp, 1-0

109

$\frac{R}{k} \cdot kc + \left(\frac{R}{k} + \frac{R}{k}\right)(3k + \beta)c$  $RC + 2\frac{R}{K}(3K+p)C$ RC + GRC + ZRBC FRC + fr ZRC LEFFORT DELAY: DEPENDS ON COMPLEXITY OF GATE, PSIZE OF GATE, AND WAST IT IS DRIVING PARASITIC DELAY : INNEVENT Delay when no LOAD is ATTACLED, INDEPENDENT OF SIZING NOTE: INCREASING B, INCREASES effort DELAY INCREASING K, DECREASES EFFORT DELAY BUT WILL INCREASE A OF PREVIOUS GATE!

ECE 5745

1

5

Antional Brand access

-

-

-

-

50

12

ECE S745

A National Brand

-

ECE SZYS

A2-301 A2-302 A2-302 A2-302 A2-300

109

ECE STYS

A National®Brand 42881 10844

15

MANY, MANY APPROXIMATIONS - ELMONE DELAY - p=1 for inv (ie. Imm out cap ~ Imm gave cap) - Ignore internal parasine cap - equal Rice 20 fail mme - Mp = 2Mm - Ignone Acrual rice (fail mmes - Ignore INPUT Arrival Time - Ignone velocity sanration Still Reasonably good Results when using logical effort for sizing even in modern technologies Helps Designers Build the Right WINITION

ECE S745

(

50

5

### 109

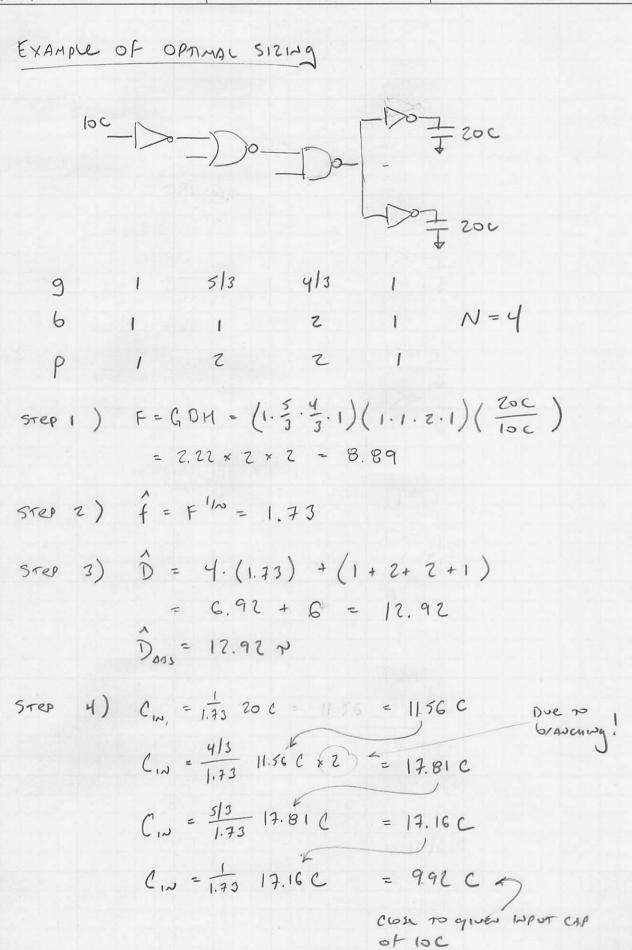

So for Above example:

$$G = 1 \cdot \frac{5}{3} \cdot \frac{7}{3} \cdot 1 = 20/9 = 2.22$$

$H = 200/100 = 2$

PATH EFFORT is me product of stage efforts

F=TTf,=TTg.h;

ECC 5345

ECC 5345

ECC 5345

ECC 5345

To Since stage ethan

$$f = gh$$

, Does pan diant  $F = Gh$ ?

Constituent simple example:

$f = 1 + 1 = 1$

$f = 1 + 1 = 1$

A National Brand Asses Solvers EVE-EXE\* - 5 SOLVERS

SC

NOTE MAT PAM étént péderos ou circuit topology and loading of entire PAM BUT NOT Sile of TRANSITIONS IN NETWORK AUSO NOTE MAT PAM étént Does not change if ADD or remove inverters! ECE STUS

-

ĒC

-

#### 709

18 WIM THESE METRICS WE CAN NOW ANSWER THE THO early Quesnows. Q1: NOW SHOULD WE SILE GATES TO MINIMINE TOTAL DELAY? START WIM PAM DELAY EQUATION: D= Idi = Zghi + Zpi independent variables are h's (i.e. whereal gate sinnings). we what to choose his to normile D. So we can take me partial serviciative of D wim respect to his, set to zero, AND solve for opponum his. CIAR 2 - C3 GATC Gasider no stage parm Assume C, AUD C3 WPUT CAP C, Cz Are gives logical eff 3. 92 Parasitic Roly Pi 12  $D = (q,h,+p,) + (q_{2}h_{2} + p_{2})$ NOTE THAT h, AND hz are constrained since (1 AD Co are gives and input cap of gave 2 is output cap for yoke 1  $h_{1} = C_{2}/C_{1}, \quad h_{2} = C_{3}/C_{2}$ H = h,hz = C3 H is A CONTANT SIJCE C, AND C3 given Substinute hz = H/hi wto Decay eauATION  $D = (g, h, + p,) + (\frac{g_2 H}{h} + p_2)$

ECE 5745

A National Brand acoust so settistic texters - s

.

-

The PANNAL Derivative with respect to only variable h,

$$\frac{dD}{dh_{1}} = g_{1} - \frac{g_{2}H}{h_{1}^{2}} = 0$$

$$g_{1}h_{1}^{2} = g_{2}H$$

$$g_{1}h_{1}^{2} = g_{2}H$$

$$g_{1}h_{1}^{2} = g_{2}h_{1}$$

$$g_{1}h_{1}^{2} = g_{2}h_{2}$$

$$g_{1}h_{1}^{2} = g_{2}h_{2}$$

$$g_{1}h_{1}^{2} = g_{2}h_{2}$$

$$g_{1}h_{1} = f_{2}$$

This goveralizes to lands with any humber of stages!

SAME in born stages!

SAME is born stages!

SAME is born stages!

for a gareral part, optimal Decay is:

$$\hat{f} = F^{1/3}$$

Take Array can effort in each stage.

$$\hat{D} = N F^{1/3} + P$$

Min Park being of optimal sizing

Memob for optimal Sizing

1. Calculate park effort for each stage  $\hat{f} = F^{1/3}$

3. Estimate min being of  $p = N\hat{f} + p$

4. Starting with unit stage, work sale array each gave

$$\hat{f} = gh = g \frac{f_{0}}{f_{0}}$$

$$C_{m} = \frac{9}{\hat{f}} C_{m}$$

## ECE 5745

5

Antional Brand 42302 10

709

ECE STYS

-

A2001 1 42-001 1 42-001 2

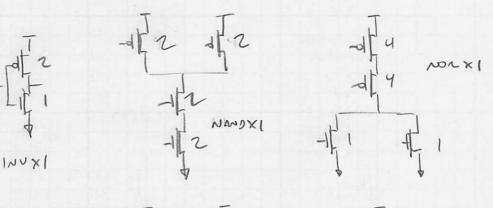

This Assumes we can sile gate Arbitrarily IN A FULL WITOM. Design. WHAT IF USING STANDARD Cell LIB?

ASSUME STANDARD Cell LIB WIM Following JAtes INVXI, INVX2 INVX3 INVX4 INVX5 INVX6 NANDXI NANDX2 NANDX4 NONXI NONX2 NONX4

Drive strength of AN XI INVENTER. SO NANDX2 MEANS d=2

Assume we usue Reternines optimal sizing is Cin, how Do we figure out which cell to use?

neverber

$$g = \frac{R_{t}C_{t}}{R_{t}N_{t}C_{t}N_{t}}$$

it we assume  $R_{t} = R_{t}N_{t}N_{t}$

$g = C_{t}/C_{t}N_{t} \longrightarrow C_{t} = gC_{t}N_{t}$

AND  $C_{1N} = dC_{t}$

$f = C_{1N} = dgC_{t}N_{t}$

$d = C_{1N} = dgC_{t}N_{t}$

$d = C_{1N} = C_{t}N_{t}$

ECESTUS

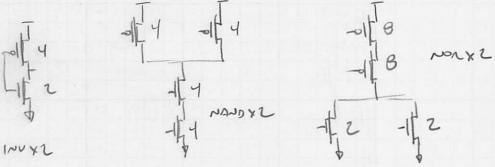

| Gives opinion           | Cia tron                                                                   | 1 Betore,    | what is a                                    | ?                |

|-------------------------|----------------------------------------------------------------------------|--------------|----------------------------------------------|------------------|

| Ciw                     | 9                                                                          | d            |                                              | gare?            |

| 11.56 C                 | 1 11.5                                                                     | 6/(1.3)      | = 3.85                                       | 1222             |

| 17.81 C                 | 4/3 17.                                                                    | 81/(4.3)     | = 4.43                                       | NANDXY           |

| 17.16 C                 | 5/3 17.                                                                    | 16 / (= 3,3) | = 3.55                                       | NONXY            |

| 9.92 C                  | 1 9.4                                                                      | 12/(1.3)     | = 33                                         | > EXUM           |

|                         |                                                                            | MUIT         | be 410C for                                  | NPUT CONSTRAINT) |

| NONXY CI.<br>NAVOXY CI. | $\frac{2}{2} \propto g 3C$ $= \alpha g 3C$ $= \alpha g 3C$ $= \alpha g 3C$ |              | sto cell gi<br>c = 12C<br>z = 16C<br>z = 70C | ATC              |

| NOW use PAN             | n Reisy                                                                    | EQUATION     |                                              |                  |

|                         | + (4.12×2                                                                  |              | $+(1.\frac{25}{9})+($<br>+ 7.22 +            |                  |

= 7.22 + 6

= 13.22

Compare win opping which is 12.92 off by 2.390

ECE 5745 23 109 Q2: How Shows we change prology to minine Delay? Assume WE WANT TO IMPLEMENT AN RIGHT INPUT AND gare. CALCULATE Alminum Delay Assuming Optimal siling for following mee ropologies assuming H=1 and H=12 (0) A2381 500 10/3 510 2 1 9 9 B 4 2 P P 5/3 4/3 g 43 1 2 2 2 P 1 H= 12 H=1 10 ·D Topology NE'IN NFIL P P 12.65 B-NAND 3.65 9 12.64 9 21.64 3.65 6 9.65 12.64 2× 4-NAND 18.64 6 5.25 12.25 4x 2-NAND 7 7 16.77 9.77

-

ECE STYS

42-381 50 SHEETS 42-381 50 SHEETS 42-382 100 SHEETS

## 709

OF 3,59 when we take into Account PARASITICS. We can roughly Approximate 3.59 to be 4

ECES7415

A National Brand 4200 00 HETTS EVELAGE\* 5 SOUMES

$F^{\frac{1}{2}} = 4$   $\log (F^{\frac{1}{2}}) = \log (4)$   $\frac{1}{2} \log (F) = \log (4)$   $\hat{\Lambda} = \frac{\log (F)}{\log (F)} = \log_{4} (F)$

So oppmar number of stages For whether chain is Roughly:

Since G=1 AND B=1 for insuter endin

N = (0gy (H)

NOT TOO 13AD OF AN RESTIMATE EVED FOR REALISTIC PATTS ON GATES THAT ARE NOT INVESTERS

### ECE STYS

A National Brand

Logical ettort CAN help give is intuition on How To Size gates + choose A topology to minimue zelay bit IT was mary initations.

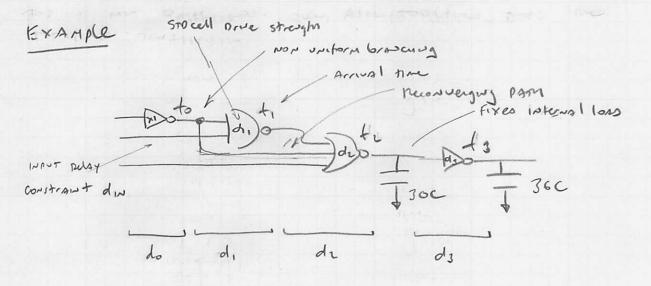

to Deal with more complights scenarios we can also write the Delay equations for each gate in system and minimum the latest arrival time.

lot's write our linear rolay equations as a function of d

$$d = gh + \rho \qquad g = \frac{R_{T}C_{T}}{\sqrt{m_{T}C_{T}}} \qquad C_{W} = d(C_{T}) \qquad C_{T} = \frac{C_{T}}{d}$$

$$d = \frac{C_{W}}{dC_{W}} \cdot \frac{C_{T}}{C_{W}} + \rho \qquad g = \frac{C_{W}}{dC_{W}}$$

$$= \frac{C_{W}}{dC_{W}} \cdot \frac{C_{W}}{C_{W}} + \rho \qquad g = \frac{C_{W}}{dC_{W}}$$

$$= \frac{C_{W}}{dC_{W}} \cdot \frac{C_{W}}{C_{W}} + \rho \qquad g = \frac{C_{W}}{dC_{W}}$$

recall Cw = 3gd

26

& (sto cell orive)

ECIE SAYS

42-801 SO SHEETS EVELASE\* 5 SOUMES 42-802 TO SHEETS EVELASE\* 5 SOUMES 42-802 TO SHEETS EVELASE\* 5 SOUMES 42-802 200 SHEETS EVELASE\* 5 SOUMES

-

Now write news for even strage

$$\frac{d_0}{d_1} = \frac{d_1}{d_2} = \frac{d_2}{d_3}$$

$$\frac{d_2}{d_1} = \frac{d_1}{d_1} = \frac{d_2}{d_2} = \frac{d_3}{d_3}$$

$$\frac{d_1}{d_1} = \frac{d_1}{d_1} = \frac{d_2}{d_2} = \frac{d_3}{d_3}$$

$$\frac{d_1}{d_1} = \frac{d_1}{d_1} = \frac{d_2}{d_1} = \frac{d_3}{d_1} = \frac{d_3}{d_2} = 1$$

$$\frac{d_2}{d_1} = \frac{(4d_1 + 7d_2)}{3 \cdot d_1} = 1 = \frac{d_1}{3}d_1 + \frac{d_2}{3}d_2 + 1$$

$$\frac{d_3}{d_1} = \frac{(7d_2)}{3 \cdot d_1} + 2 = \frac{7}{3}\frac{d_2}{d_1} + 2$$

$$\frac{d_2}{d_2} = \frac{(7d_2 + 3d_3)}{3 \cdot d_2} + 3 = \frac{10}{d_2} + \frac{d_3}{d_2} + 3$$

$$\frac{d_3}{d_1} = \frac{(36)}{3 \cdot d_3} + 1 = \frac{12}{d_3} + 1$$

$$\frac{Arrival Tries}{f_0 = d_0}$$

$$\frac{f_0}{f_1} = \frac{f_1}{3 \cdot d_3} + \frac{d_2}{f_2} + \frac{d_3}{f_3}$$

$$\frac{f_1}{f_2} = \frac{f_1}{f_2} + \frac{d_3}{f_3}$$

ECE 5745

Actional Brand Action 1

tz = MAX ( do, MX ( do, dw) + d, ) + dz + dz

MINIMIRE to subject to above constraints with OI, dr do as the independent variables

Acrually in synthesis we really what to minute AREA (on every) Subject to constraint on ty.

so ve could craft of militarios problem to be mulmiter som of d, dz dz (prox/for Anen) subject to constraint:

$t_{clk} > max (do, max (do, din) + din) + dz + dz$

( S CLOCK PERIOD CONSTRANT

20

| ECESTRUS                                | 109                                                                                    |

|-----------------------------------------|----------------------------------------------------------------------------------------|

| ENergy                                  |                                                                                        |

| Everyy is A measure                     | ot work                                                                                |

| power is me rate                        | AT which work is DONE                                                                  |

| + + + + + + + + + + + + + + + + + + + + |                                                                                        |

| E field                                 |                                                                                        |

| LILO III test o                         | rge Electrical por erega                                                               |

| W 5M                                    | mil electrical por everyy                                                              |

| Electric Pot every                      | CAPACINY ten Doing work which<br>Arrives from positions of charge<br>IN Efield (TONES) |

| RELEATIC POTENTIAL                      | ELECTRIC POT ENERGY of A POSITION<br>PER UNIT CHARGE                                   |

|                                         | (volts, IV=IJ/C,) AV=DE/Q)                                                             |

| CURIENT                                 | NATE AT WHICH CHArge to-s PAST<br>POSITION                                             |

|                                         | (AMPS, IA = ICS, I=Qlot)                                                               |

| pown                                    | NATE AT WHICH ELECTRIC EVERY<br>15 Supplies of consumes                                |

|                                         | (WATTS, IW = IJIS, P=DE/At                                                             |

| P                                       | $= \frac{\Delta V \cdot Q}{Q/I} = VI$                                                  |

| Man                                     | $E = \int_{0}^{T} P(t) dt$                                                             |

| Evergy                                  | 12                                                                                     |

|                                         |                                                                                        |

Assi 50 SHEETS EVERNE 2010 SHEETS EVERNE 2020 TO SHEETS EVERNE 2020 SHEETS EVERNE

80

.

ECE STAYS 31 Power Prot = PSWITCHING + PSTATIC = of f 2 CV da + Vdd Ioff 45. Antional<sup>®</sup>Brand 42.00 NHEERS EVEEASE\* - 5 SOUN - 100 NHEERS EVEEASE\* - 5 SOUNN - 2.00 NHEERS EVEEASE\* - 5 SOUNN L'é # traditions, sometimes duit # 1-20 traditions but mes won't be faiton of É interes of forcing.

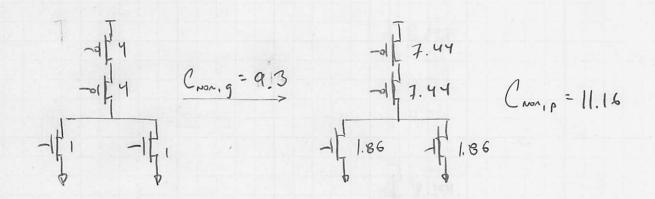

# ECE STYS 32 Compare Energy Nees to Find TOTAL SUITCHES CAP IN WORST CASE TIOC 2 5/3 10/3 I A National Brand action to 9 4 2 B 1 P 10/3 10/3 G H B 1 10/3 F 1013

1 f 1.8 1.8

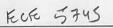

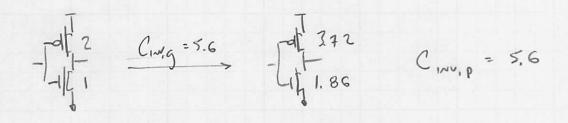

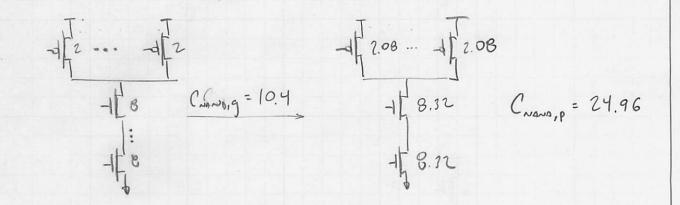

$C_{NV,g} = \frac{1}{1.8} 10 = 5.6 \qquad C_{NON,1g} = \frac{513}{1.8} 10 = 9.3$   $C_{NANO,g} = \frac{1013}{1.8} 5.6 = 10.4 \qquad C_{NON,0} = \frac{2}{1.8} 9.3 = 10.3$   $C_{TOT,g} = C_{NV,g} + B \cdot C_{NAND,0} \qquad C_{TOT,g} = 2C_{NOT,g} + 8C_{NANd,0}$   $= 88.8 C \qquad = 101 C$

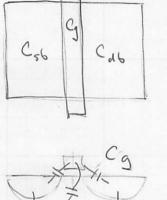

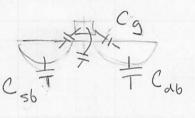

To Determine PARASITIC CAP Need to UNDENSTAND NOW GATE CAP IS DISTRIBUTED ACTOSS TRANSISTANS.

A National Brand

-

ĒC

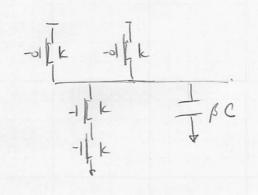

inverter

B WOUT NAND GATE

2 INDUT NON GATE

MINDUT NAND GATE

$-d_{1}^{2} - d_{1}^{2} - d_{$

K

EASE® - 5 SOU EASE® - 5 SOU EASE® - 5 SOU

-

$$\frac{1}{4} = \frac{1}{2} \left( \frac{1}{2} \sqrt{4a^2}, \frac{1}{2} \right) \frac{1}{2} \sqrt{4a^2}, \frac{1}{2} \right) \frac{1}{2} \sqrt{4a^2}, \frac{1}{2} \right) \frac{1}{2} \sqrt{4a^2}, \frac{1}{2} \right) \frac{1}{2} \sqrt{4a^2}, \frac{1}{2}$$

1 500 MUZ

KEE 5745

ACTIVITY FALTONS

- PREVIOUS EXAMPLE JUST UND FIXED OF 0.1 For all NOTES.

- MORE ACCURATE TO TRACK ACTIVITY FALTONS TWO TOPOlogy

$$= D_{D-DO} = D_{D-D} =$$

42%. SHEFTS EVE 445<sup>4</sup> - 1 SOUN 42%. SHEFTS EVE 445<sup>4</sup> - 1 SOUN 42:302 : 00 SHEFTS EVE 445<sup>4</sup> - 1 SOUNRES ECE STUS

NANDZ Probability output is zero NANDZ Piper = (PAPS)(I-PAPS) = Probability output is one

omenuise areas of Name 2 is zero it bom inputs one

12 Assume INPUTS, Are 12000 DATA

$P_{A} = 0.5 \quad P_{B} = 0.5$   $(A_{OVT}' = (P_{A}P_{B})(1 - P_{A}P_{B}) = (0.5 \times 0.5)(1 - 0.5 \times 0.5)$   $= (0.25)(1 - 0.25) = 0.25 \times 0.75 = 0.6$

NANO 8

A National Brand 42382 100

$d_{our}' = \overline{P_{our}P_{our}} = \left(P_{i,v}^{B}\right)\left(1 - P_{i,v}^{B}\right)$

OUTPUT IS OTHER LES IF all B MANTS Are one OMENILE OUTPUT OF NANDE IS ONE

$\alpha_{our}' = (P_{in}^{8})(1 - P_{in}^{8}) = (0.5^{8})(1 - 0.5^{8})$ = (0.0039)(0.996) = 0.0039

During lecture today, I mentioned that \_adding\_ inverters can sometimes \_reduce\_ the path delay. This might seems counter intuitive based on what you learned in ECE 2300. In ECE 2300, gates had a \_constant\_ delay. So every inverter might always have a delay of 1 tau, and every NAND2 gate might always have a delay of 2 tau. In fact, we used a similar simplification when estimating the critical path in ECE 4750. If we assume a constant delay model, then adding a pair of inverters would indeed \_always\_ slow down the path delay. Adding a pair of inverters would simply increase the total propagation delay.

Based on what we have learned in ECE 5745 so far, it should be clear that the constant delay model is a significant oversimplication. The delay of a gate depends on many things including its size, the load capactance at the output, when inputs arrive, the rise/fall time of the inputs, layout details, etc. Our RC modeling and method of logical effort use a \_linear\_ delay model which is a little more reasonable than a \_constant\_ delay model (but of course is still a significant simplification!). So the delay of a gate is:

d = gh + p

The logical effort (g) and the parasitic delay (p) depend only on the template, while the electrical effort (h) depends on both the size of the gate (Cin) and the load capacitance at the output (Cout).

Let's look in more detail at the example we were discussing in lecture to demonstrate how \_adding\_ intervers can sometimes \_reduce\_ the path delay. Assume after synthesis we have the following two-gate path:

So we have a X1 two-input NAND gate (NAND2X1) and a X4 inverter driving a load of 1000C. The synthesis tool optimized the design assuming the inverter was driving a modest load, but after place-and-route, it turned out that the inverter has to drive a cross-chip global wire and thus a very large fixed capacitance.

What is the delay of this two-gate path?

D = ( g0\*h0 + g1\*h1 ) + ( p0 + p1 ) = ( 4/3 \* 12/4 + 1 \* 1000/12 ) + ( 2 + 1 ) = ( 4 + 83.3 ) + 3 = 90.3 tau

Recall that the minimum delay will occur when the stage effort is equal across all stages. Notice that the stage effort of the two stages is not even close to being equal which suggests this sizing is suboptimal.

The place-and-route tool can potentially reduce the path delay using "buffer resizing". So let's assume the tool wants to increase the size of the inverter. Let's use logical effort to figure out the optimal sizing.

F = GHB = 4/3 \* 1000/4 \* 1 = 333f' = F^(1/N) = (333)^(1/2) = 18.25 D' = N\*F^(1/N) + P = 2\*18.25 + (2 + 1) = 39.5 tau Note that I am using f' instead of f "hat" and D' instead of D "hat". The path delay is significatly lower if we can resize the inverter. Let's figure out how large the final inverter needs to be to achieve this optimal delay.

C in, 1 = (q/f') \* C load = (1/18.25) \* 1000 = 54.8C

That is a pretty big inverter! The inverter's NMOS would be 18.27 times the minimum width and the inverter's PMOS would be 36.53 times the minimum width. Assume our standard cell library has an INVX1, INVX2, INVX4, INVX8, INVX16, INVX32, and INVX64. Let's choose the INVX16 for the final inverter (which is a little smaller than the optimal full-custom sizing).

--|NAND |NAND---I>0------|NAND | 4C --- 1000C NAND2X1 INVX16 ---| V

What is the new delay of the new path?

D = ( g0\*h0 + g1\*h1 ) + ( p0 + p1 ) = ( 4/3 \* 48/4 + 1 \* 1000/48 ) + ( 2 + 1 ) = ( 16 + 20.8 ) + 3 = 39.8 tau

The delay using the standard cell is a little slower and the stage effort is not exactly balanced, but buffer resizing does still significantly reduce the path delay.

The place-and-route tool can potentially further reduce the path delay using "buffer insertion". Let's quickly estimate the optimal number of stages.

$\log 4(F) = \log 4(333) = 4.2$

So the rough estimate of the optimal number of stages if 4, but we are only using two stages. Let's add two INVX1 gates at the end of the path to see if that helps.

-- | NAND | NAND---I>o----I>o----I>o------ | NAND 4C NAND2X1 INVX16 INVX1 INVX1 ---| V D = ( g0\*h0 + g1\*h1 + g2\*h2 + g3\*h3 ) + ( p0 + p1 + p2 + p3 ) = ( 4/3 \* 48/4 + 1 \* 3/48 + 1 \* 3/3 + 1 \* 1000/3 ) + ( 2 + 1 + 1 + 1 ) = ( 16 + 0.0625 + 1 + 333.3 ) + 5 = 355 tau

Yeow -- this is a bad idea. The delay is 9x worse! Instead of driving the large load capacitance with an INVX16, now we are driving this large load capacitance with an INVX1. Very bad idea. What if we add two more INVX16 gates at the end of the path?

#### ece5745-buf-resizing-insertion.txt

```

-- | NAND

| NAND---I>0----I>0----I>0-----

-- | NAND

4C

NAND2X1 INVX16 INVX16 INVX16 ----

|

V

D = ( g0*h0 + g1*h1 + g2*h2 + g3*h3) + ( p0 + p1 + p2 + p3)

= ( 4/3 * 48/4 + 1 * 48/48 + 1 * 48/48 + 1 * 1000/48) + ( 2 + 1 + 1 + 1

)

= ( 16 + 1 + 1 + 20.8) + 5

= 43.8 \text{ tau}

```

This is better than the original design, but slower than the optimized two-gate design with buffer resizing. The key is that we don't want to add more inverters. We want to add more inverters and then properly resize the gates to ensure we are balancing the stage efforts appropriately. We can just use the method of logical effort to find the optimal delay and the optimal sizing.

F = GHB = 4/3 \* 1000/4 \* 1 = 333f' = F^(1/N) = (333)^(1/4) = 4.27 D' = N\*F^(1/N) + P = 4\*4.27 + (2 + 1 + 1 + 1) = 22.1 tau

So we have further reduced the delay by using a combination of buffer insertion and buffer resizing. Let's figure out how large each inverter needs to be to achieve this optimal delay.

C\_in,3 = (g/f') \* C\_load = (1/4.27) \* 1000 = 234C C\_in,2 = (g/f') \* C\_in,3 = (1/4.27) \* 234 = 55C C\_in,1 = (g/f') \* C\_in,2 = (1/4.27) \* 55 = 13C

Yeow -- that is a big final inverter! Our INVX64 has a C\_in of 192C so that will be the best we can do. Let's size our inverters as follows:

-- | NAND | NAND---I>0----I>0----I>0------ | NAND 4C --- 1000C NAND2X1 INVX16 INVX32 INVX64 ---| V

And now let's calculate the delay again:

```

D = ( g0*h0 + g1*h1 + g2*h2 + g3*h3 ) + ( p0 + p1 + p2 + p3 )

= ( 4/3 * 48/4 + 1 * 96/48 + 1 * 192/96 + 1 * 1000/192 ) + ( 2 + 1 + 1 +

1 )

= ( 16 + 2 + 2 + 5.2 ) + 5

= 27.2 tau

```

The original design without buffer insertion/resizing had a delay of 90.3 tau while the new design with buffer insertion/resizing has a delay of only 27.2, and improvement of 3.3x! So clearly \_adding\_ inverters can \_reduce\_ the path delay, but (as we saw with some of our counter-examples) this is only true if you properly size the gates!

#### ece5745-freepdk45nm-process.txt

It is useful in our pen-and-paper analysis to have a good estimate for some of the technology parameters in our target process. For example, when estimating the power and energy of a circuit, we need to know the supply voltage and gate capacitance (since all of our switched capacitance estimtes will be in units of C). West & Harris provides a methodology for using SPICE simulations to estimate various technology parameters. We can also look in the .lib file for our 45nm standard cell library, since this file was itself generated from many SPICE simulations.

The following snippet shows the entry in the .lib file for our cannonical inverter (INV\_X1). We can see that the nominal supply voltages is 1.1V and that the total input gate capacitance for this inverter is estimated to be 1.7fF.

```

library (NangateOpenCellLibrary) {

. . .

/* Units Attributes */

time_unit

: "1ns";

: "1nW";

leakage_power_unit

Voltage_unit

: "1V";

: "1mA";

current_unit

pulling_resistance_unit : "1kohm";

capacitive_load_unit

(1,ff);

/* Op Conditions */

: 1.00;

nom_process

: 25.00;

nom_temperature

nom_voltage

: 1.10;

Module : INV_X1

Cell Descr : Combinational cell (INV_X1) with drive strength X1

cell (INV_X1) {

drive_strength

: 1;

: 0.532000;

area

. . .

pin (A) {

direction

: input;

related_power_pin : "VDD";

related_ground_pin : "VSS";

capacitance : 1.700230;

fall_capacitance : 1.549360;

rise_capacitance : 1.700230;

}

. . .

```

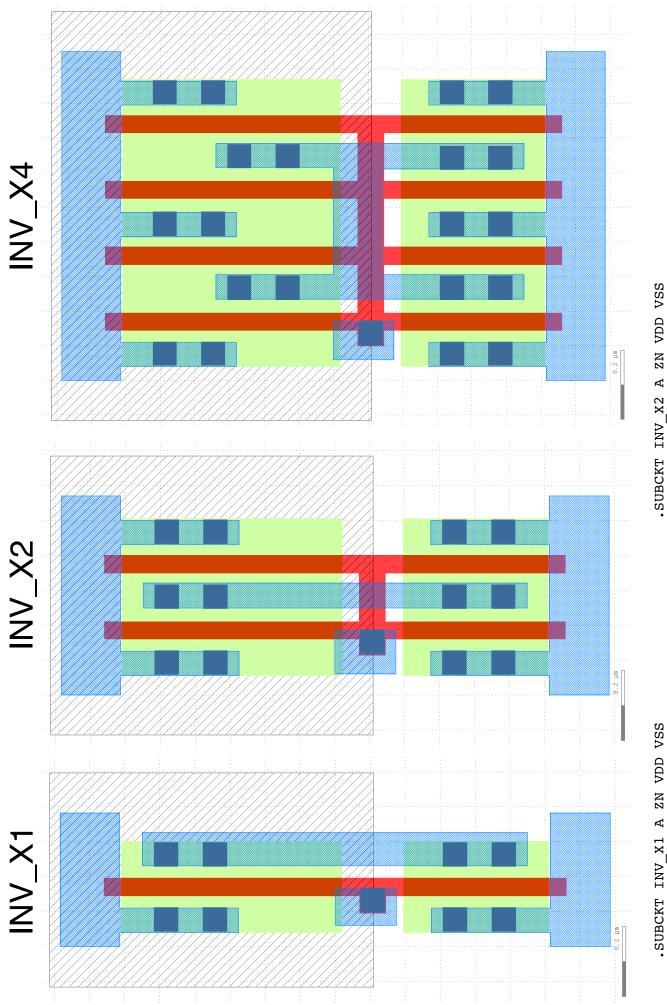

However, we need an estimate for C which is the gate cap for the NMOS in this cannonical inverter. We can figure out C if we take a closer look at the layout and SPICE deck for this inverter. The following page shows the layout for an INV\_X1, INV\_X2, and INV\_X4 gate along with the corresponding SPICE deck for an INV\_X1 and INV\_X2 gate.

Notice how the layout uses multiple parallel "fingers" to implement a single larger "logical" transistor. So an X2 gate has two fingers and an X4 has four fingers. The SPICE deck has the exact length and width of each transistors (we could also just measure the layout). Notice that both transistors have a width of 50nm even though this is a 45nm process! It is not unsual for standard-cell libraries to use slightly longer than

#### ece5745-freepdk45nm-process.txt

minimum transistors, since this geometry offers a nice compromise between performance and power consumption. The PMOS width is 630nm and the NMOS width is 415nm. Notice that the PMOS is definitely not twice the width of the NMOS (it is only 630/415 = 1.5x). This is probably because the mobility of an NMOS transistor is not exactly 2x the mobility of a PMOS transistor, and also because the standard-cell library is choosing to offer slightly unequal rise/fall times to offer reduced energy and area. Also notice that the NMOS in this inverter is 415/45 is about 9x the technology node size. This is ratio is a very reasonable size.

With this information we can now estimate C. We know the total gate cap for an INV\_X1 gate is 1.7fF, and we know the ratio of how much of that gate cap comes from the NMOS is 415/(415+630) = 0.4. So C is  $0.4 \times 1.7fF$ = 0.68fF. To make our analysis simpler we will just roughly estimate the supply voltage as 1V and C as 0.5fF.

\*.PININFO A:I ZN:O VDD:P VSS:G \*.EQN ZN=!A M\_i\_O ZN A VSS VSS NMOS\_VTL W=0.415U L=0.050U M\_i\_1 ZN A VDD VDD PMOS\_VTL W=0.630U L=0.050U .ENDS

.SUBCKT INV\_X2 A ZN VDD VSS \*.PININFO A:I ZN:O VDD:P VSS:G \*.EQN ZN=!A

M\_i\_0\_0\_x2\_0 ZN A VSS VSS NMOS\_VTL W=0.415U L=0.050U M\_i\_0\_0\_x2\_1 VSS A ZN VSS NMOS\_VTL W=0.415U L=0.050U M\_i\_1\_0\_x2\_0 ZN A VDD VDD PMOS\_VTL W=0.630U L=0.050U M\_i\_1\_0\_x2\_1 VDD A ZN VDD PMOS\_VTL W=0.630U L=0.050U .ENDS