Cornell University

School of Electrical and Computer Engineering

ECE 5745 Complex Digital ASIC Design

Spring 2023

Prof. Christopher Batten

407 Phillips Hall • Tuesday and Thursday • 1:00–2:15pm

home | syllabus | schedule | readings | handouts | resources

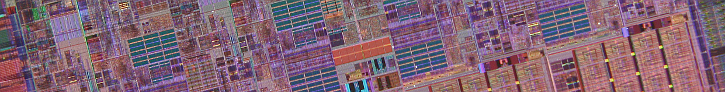

This course aims to provide a strong foundation for students to understand the principle and practice of designing, implementing, testing, and evaluating complex standard-cell ASIC chips using automated state-of-the-art electronic design automation (EDA) tools. This course is at the intersection of computer architecture, digital circuits, and EDA and is suitable for students pursuing careers in both research and industry. For students pursuing research topics in computer architecture, the course will provide deeper insight into critical physical design issues for future computing systems, while for students pursuing research topics in digital circuits, the course will provide system-level insight into future large-scale chip designs. For students pursuing a career in the chip-design industry, the course will provide valuable design experience from architecture to digital circuits.

The course is divided into four parts: the first three parts are lecture-based, while the final part is an extensive design project. The first part provides an overview of ASIC design including: hardware description languages; CMOS devices; CMOS circuits; full-custom design methodology; automated design methodologies; testing and verification; packaging and I/O. The second part provides a deeper study of CMOS digital-circuit fundamentals including combinational logic, sequential state, and interconnect. The third part provides a deeper study of EDA algorithms including synthesis algorithms and physical design automation algorithms. The final part is an open-ended design project where small groups of students design, implement, test, and evaluate an interesting technique in computer architecture using functional-, microarchitectural-, register-transfer-, and layout-level modeling. This five-week long design experience will include weekly project meetings with the course instructors, milestone documents, a project demonstration, and a detailed final report.